Category:Kunal R. Parekh of Boise ID (US)

Kunal R. Parekh of Boise ID (US)

Executive Summary

Kunal R. Parekh of Boise ID (US) is an inventor who has filed 10 patents. Their primary areas of innovation include SEMICONDUCTOR DEVICES NOT COVERED BY CLASS (6 patents), {Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected} (5 patents), SEMICONDUCTOR DEVICES NOT COVERED BY CLASS (5 patents), and they have worked with companies such as Micron Technology, Inc. (10 patents). Their most frequent collaborators include (4 collaborations), (3 collaborations), (3 collaborations).

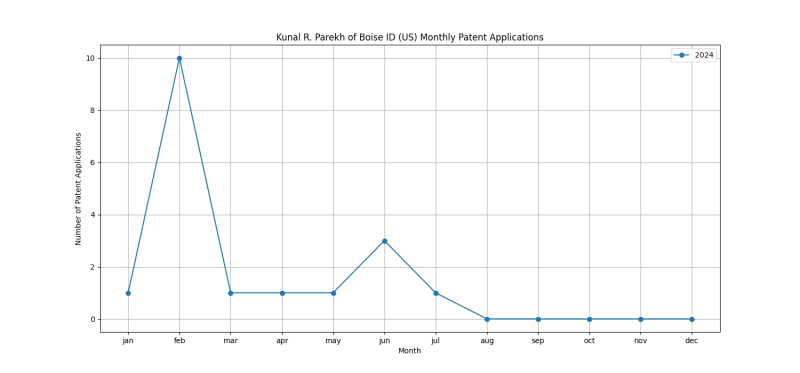

Patent Filing Activity

Technology Areas

Error creating thumbnail: File missing

List of Technology Areas

- H01L24/08 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 6 patents

- H01L24/80 ({Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected}): 5 patents

- H01L25/0657 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 5 patents

- H01L25/18 (the devices being of types provided for in two or more different subgroups of the same main group of groups): 5 patents

- H01L2224/80895 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 5 patents

- H01L2224/80896 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 5 patents

- H01L2924/1431 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 5 patents

- H10B80/00 (Assemblies of multiple devices comprising at least one memory device covered by this subclass): 5 patents

- H01L25/50 ({Multistep manufacturing processes of assemblies consisting of devices, each device being of a type provided for in group): 4 patents

- H01L2924/1436 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 4 patents

- H01L2224/08146 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 4 patents

- H01L25/0652 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 3 patents

- H01L2224/08145 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 3 patents

- H01L2225/06541 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 3 patents

- H01L2225/06589 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 3 patents

- G11C11/4093 (Input/output [I/O] data interface arrangements, e.g. data buffers): 2 patents

- G06F3/0656 ({Data buffering arrangements}): 2 patents

- G06F13/1673 (ELECTRIC DIGITAL DATA PROCESSING (computer systems based on specific computational models): 2 patents

- G06F13/28 (using burst mode transfer, e.g. direct memory access {DMA}, cycle steal (): 2 patents

- G11C7/08 (Control thereof): 2 patents

- G11C7/1039 ({using pipelining techniques, i.e. using latches between functional memory parts, e.g. row/column decoders, I/O buffers, sense amplifiers}): 2 patents

- G11C11/4087 ({Address decoders, e.g. bit - or word line decoders; Multiple line decoders}): 2 patents

- G11C11/4091 (Sense or sense/refresh amplifiers, or associated sense circuitry, e.g. for coupled bit-line precharging, equalising or isolating): 2 patents

- G11C11/4096 (Input/output [I/O] data management or control circuits, e.g. reading or writing circuits, I/O drivers or bit-line switches): 2 patents

- G16B30/00 (ICT specially adapted for sequence analysis involving nucleotides or amino acids): 2 patents

- G16B50/10 (BIOINFORMATICS, i.e. INFORMATION AND COMMUNICATION TECHNOLOGY [ICT] SPECIALLY ADAPTED FOR GENETIC OR PROTEIN-RELATED DATA PROCESSING IN COMPUTATIONAL MOLECULAR BIOLOGY): 2 patents

- H01L21/78 (with subsequent division of the substrate into plural individual devices (cutting to change the surface-physical characteristics or shape of semiconductor bodies): 2 patents

- H01L22/12 ({for structural parameters, e.g. thickness, line width, refractive index, temperature, warp, bond strength, defects, optical inspection, electrical measurement of structural dimensions, metallurgic measurement of diffusions (electrical measurement of diffusions): 2 patents

- H01L24/48 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- G06F2213/28 (ELECTRIC DIGITAL DATA PROCESSING (computer systems based on specific computational models): 2 patents

- H01L24/16 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L2224/0801 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L2224/1601 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L2224/16221 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L2224/48091 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L2224/48145 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L2224/48221 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L2225/06517 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L2225/06524 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L2225/06527 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L2225/06565 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L2924/14335 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L2225/06544 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L2924/1434 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L23/481 (Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements {; Selection of materials therefor}): 2 patents

- H10B43/27 (ELECTRONIC MEMORY DEVICES): 2 patents

- H01L24/05 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L2225/06548 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2225/06586 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L23/5384 ({Conductive vias through the substrate with or without pins, e.g. buried coaxial conductors (): 1 patents

- H01L21/50 (Assembly of semiconductor devices using processes or apparatus not provided for in a single one of the subgroups): 1 patents

- H01L21/76802 (Applying interconnections to be used for carrying current between separate components within a device {comprising conductors and dielectrics}): 1 patents

- H01L21/76877 ({Thin films associated with contacts of capacitors}): 1 patents

- H01L23/5386 (the interconnection structure between a plurality of semiconductor chips being formed on, or in, insulating substrates ({): 1 patents

- H01L27/0688 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L27/092 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L23/49894 (Leads, {i.e. metallisations or lead-frames} on insulating substrates, {e.g. chip carriers (shape of the substrate): 1 patents

- H01L24/96 ({the devices being encapsulated in a common layer, e.g. neo-wafer or pseudo-wafer, said common layer being separable into individual assemblies after connecting}): 1 patents

- H01L24/97 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2224/96 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2224/97 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H10B41/27 (ELECTRONIC MEMORY DEVICES): 1 patents

- H10B41/35 (ELECTRONIC MEMORY DEVICES): 1 patents

- H10B43/35 (ELECTRONIC MEMORY DEVICES): 1 patents

- H01L21/304 (Mechanical treatment, e.g. grinding, polishing, cutting {(): 1 patents

- H01L21/6835 ({using temporarily an auxiliary support}): 1 patents

- H01L24/89 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L24/94 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L23/544 (Marks applied to semiconductor devices {or parts}, e.g. registration marks, {alignment structures, wafer maps (test patterns for characterising or monitoring manufacturing processes): 1 patents

- H01L2221/68368 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2223/5446 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2224/05647 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2224/89 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2224/94 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H10D30/025 (No explanation available): 1 patents

- H10D30/63 (No explanation available): 1 patents

- H10D48/36 (No explanation available): 1 patents

Companies

Error creating thumbnail: File missing

List of Companies

- Micron Technology, Inc.: 10 patents

Collaborators

- Wei Zhou of Boise ID (US) (4 collaborations)

- Akshay N. Singh of Boise ID (US) (3 collaborations)

- Bharat Bhushan (3 collaborations)

- Aliasger T. Zaidy of Seattle WA (US) (2 collaborations)

- Glen E. Hush of Boise ID (US) (2 collaborations)

- Sean S. Eilert of Penryn CA (US) (2 collaborations)

- Bret K. Street of Meridian ID (US) (2 collaborations)

- Kyle K. Kirby of Eagle ID (US) (1 collaborations)

- Albert Fayrushin of Boise ID (US) (1 collaborations)

- Haitao Liu of Boise ID (US) (1 collaborations)

- Justin B. Dorhout of Boise ID (US) (1 collaborations)

- David Daycock of Boise ID (US) (1 collaborations)

- Martin C. Roberts of Boise ID (US) (1 collaborations)

- Yushi Hu of Boise ID (US) (1 collaborations)

Subcategories

This category has the following 2 subcategories, out of 2 total.

F

K

Pages in category "Kunal R. Parekh of Boise ID (US)"

The following 38 pages are in this category, out of 38 total.

1

- 17821676. MEMORY WITH PARALLEL MAIN AND TEST INTERFACES simplified abstract (Micron Technology, Inc.)

- 17884475. SUBSTRATE FOR VERTICALLY ASSEMBLED SEMICONDUCTOR DIES simplified abstract (Micron Technology, Inc.)

- 17884484. THROUGH-SUBSTRATE CONNECTIONS FOR RECESSED SEMICONDUCTOR DIES simplified abstract (Micron Technology, Inc.)

- 18237259. SEMICONDUCTOR DEVICE WITH CIRCUIT COMPONENTS FORMED THROUGH INTER-DIE CONNECTIONS simplified abstract (Micron Technology, Inc.)

- 18315311. INTERFACES BETWEEN HIGHER VOLTAGE AND LOWER VOLTAGE WAFERS AND RELATED APPARATUSES AND METHODS simplified abstract (Micron Technology, Inc.)

- 18400745. FRONT END OF LINE INTERCONNECT STRUCTURES AND ASSOCIATED SYSTEMS AND METHODS simplified abstract (Micron Technology, Inc.)

- 18400994. TECHNIQUES FOR MODULAR DIE CONFIGURATIONS FOR MULTI-CHANNEL MEMORY simplified abstract (Micron Technology, Inc.)

- 18426271. STACKED SEMICONDUCTOR DEVICE simplified abstract (Micron Technology, Inc.)

- 18478031. MICROELECTRONIC DEVICES AND ELECTRONIC SYSTEMS simplified abstract (Micron Technology, Inc.)

- 18491711. MICROELECTRONIC DEVICES, MEMORY DEVICES, AND ELECTRONIC SYSTEMS simplified abstract (Micron Technology, Inc.)

- 18507721. FRONT END OF LINE INTERCONNECT STRUCTURES AND ASSOCIATED SYSTEMS AND METHODS simplified abstract (Micron Technology, Inc.)

- 18516734. TECHNIQUES FOR COUPLED HOST AND MEMORY DIES simplified abstract (Micron Technology, Inc.)

- 18525403. REPAIR TECHNIQUES FOR COUPLED MEMORY DIES simplified abstract (Micron Technology, Inc.)

- 18598735. TRANSISTOR ARCHITECTURES IN COUPLED SEMICONDUCTOR SYSTEMS simplified abstract (Micron Technology, Inc.)

- 18600146. MEMORY DEVICES AND RELATED METHODS OF FORMING A MEMORY DEVICE simplified abstract (Micron Technology, Inc.)

- 18610268. SEMICONDUCTOR DEVICE WITH A THROUGH DIELECTRIC VIA simplified abstract (Micron Technology, Inc.)

- 18649986. SEMICONDUCTOR WITH THROUGH-SUBSTRATE INTERCONNECT simplified abstract (Micron Technology, Inc.)

- 18674664. SEMICONDUCTOR DEVICE WITH ENHANCED THERMAL MITIGATION (Micron Technology, Inc.)

- 18676056. Integrated Assemblies and Methods of Forming Integrated Assemblies simplified abstract (Micron Technology, Inc.)

- 18815624. MEMORY DEVICES INCLUDING NON-VOLATILE MEMORY CELLS, AND RELATED MICROELECTRONIC DEVICES (Micron Technology, Inc.)

- 18818251. MEMORY DEVICES AND RELATED METHODS (Lodestar Licensing Group LLC)

- 18820840. MEMORY DEVICE FOR WAFER-ON-WAFER FORMED MEMORY AND LOGIC (Micron Technology, Inc.)

M

- Micron technology, inc. (20240176523). TECHNIQUES FOR COUPLED HOST AND MEMORY DIES simplified abstract

- Micron technology, inc. (20240186274). TECHNIQUES FOR THERMAL DISTRIBUTION IN COUPLED SEMICONDUCTOR SYSTEMS simplified abstract

- Micron technology, inc. (20240194287). REPAIR TECHNIQUES FOR COUPLED MEMORY DIES simplified abstract

- Micron technology, inc. (20240237363). TECHNIQUES FOR MODULAR DIE CONFIGURATIONS FOR MULTI-CHANNEL MEMORY simplified abstract

- Micron technology, inc. (20240282620). SEMICONDUCTOR WITH THROUGH-SUBSTRATE INTERCONNECT simplified abstract

- Micron technology, inc. (20240297149). STACKED SEMICONDUCTOR DEVICE simplified abstract

- Micron technology, inc. (20240313098). TRANSISTOR ARCHITECTURES IN COUPLED SEMICONDUCTOR SYSTEMS simplified abstract

- Micron technology, inc. (20240315018). Integrated Assemblies and Methods of Forming Integrated Assemblies simplified abstract

- Micron technology, inc. (20240339433). SEMICONDUCTOR DEVICE WITH A THROUGH DIELECTRIC VIA simplified abstract

- Micron technology, inc. (20240413021). METHOD OF MEASURING THICKNESS OF SEMICONDUCTOR WAFER AND INSPECTING BONDING VOIDS

- Micron technology, inc. (20240413145). MEMORY DEVICES INCLUDING CONTROL LOGIC REGIONS

- Micron technology, inc. (20240420757). MEMORY DEVICE FOR WAFER-ON-WAFER FORMED MEMORY AND LOGIC

- Micron technology, inc. (20240421030). SEMICONDUCTOR DEVICE WITH ENHANCED THERMAL MITIGATION

- Micron technology, inc. (20240422993). MEMORY DEVICES INCLUDING NON-VOLATILE MEMORY CELLS, AND RELATED MICROELECTRONIC DEVICES

- Wei Zhou of Boise ID (US)

- Akshay N. Singh of Boise ID (US)

- Bharat Bhushan

- Aliasger T. Zaidy of Seattle WA (US)

- Glen E. Hush of Boise ID (US)

- Sean S. Eilert of Penryn CA (US)

- Bret K. Street of Meridian ID (US)

- Kyle K. Kirby of Eagle ID (US)

- Albert Fayrushin of Boise ID (US)

- Haitao Liu of Boise ID (US)

- Justin B. Dorhout of Boise ID (US)

- David Daycock of Boise ID (US)

- Martin C. Roberts of Boise ID (US)

- Yushi Hu of Boise ID (US)

- Kunal R. Parekh of Boise ID (US)

- Inventors

- Inventors filing patents with Micron Technology, Inc.