Category:Sivagnanam Parthasarathy of Carlsbad CA (US)

Revision as of 03:23, 26 July 2024 by Wikipatents (talk | contribs) (Updating Category:Sivagnanam_Parthasarathy_of_Carlsbad_CA_(US))

Contents

Sivagnanam Parthasarathy of Carlsbad CA (US)

Executive Summary

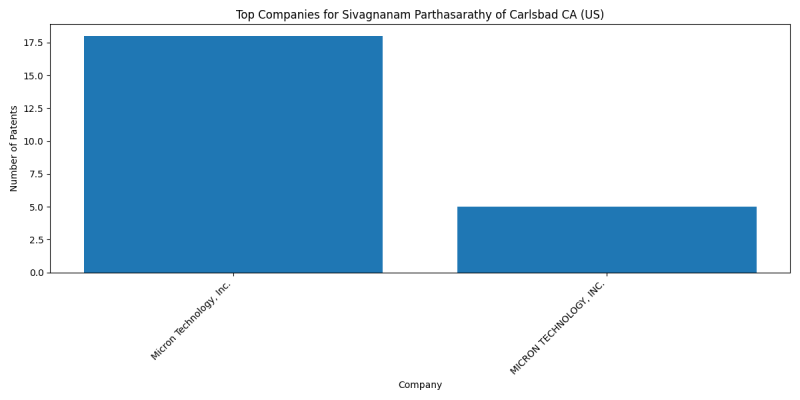

Sivagnanam Parthasarathy of Carlsbad CA (US) is an inventor who has filed 23 patents. Their primary areas of innovation include {Non-volatile semiconductor memory device, e.g. flash memory, one time programmable memory [OTP]} (6 patents), {in sector programmable memories, e.g. flash disk ( (6 patents), {in relation to data integrity, e.g. data losses, bit errors} (6 patents), and they have worked with companies such as Micron Technology, Inc. (18 patents), MICRON TECHNOLOGY, INC. (5 patents). Their most frequent collaborators include (18 collaborations), (6 collaborations), (5 collaborations).

Patent Filing Activity

Technology Areas

List of Technology Areas

- G06F3/0679 ({Non-volatile semiconductor memory device, e.g. flash memory, one time programmable memory [OTP]}): 6 patents

- G06F11/1068 ({in sector programmable memories, e.g. flash disk (): 6 patents

- G06F3/0619 ({in relation to data integrity, e.g. data losses, bit errors}): 6 patents

- G11C16/26 (Sensing or reading circuits; Data output circuits): 4 patents

- H03M13/1108 (CODING; DECODING; CODE CONVERSION IN GENERAL (using fluidic means): 4 patents

- G06F3/0655 ({Replication mechanisms}): 3 patents

- G06F11/076 (Responding to the occurrence of a fault, e.g. fault tolerance): 3 patents

- G06F3/0673 ({Single storage device}): 3 patents

- G06F3/0659 ({Command handling arrangements, e.g. command buffers, queues, command scheduling}): 3 patents

- G11C16/08 (Address circuits; Decoders; Word-line control circuits): 3 patents

- G06F3/0604 (Digital input from, or digital output to, record carriers {, e.g. RAID, emulated record carriers or networked record carriers}): 2 patents

- G06F11/1435 ({using file system or storage system metadata}): 2 patents

- G11C29/52 (STATIC STORES (semiconductor memory devices): 2 patents

- G06F3/0629 ({Configuration or reconfiguration of storage systems}): 2 patents

- G06F3/064 ({Management of blocks}): 2 patents

- G11C16/0483 ({comprising cells having several storage transistors connected in series}): 2 patents

- G06F11/0772 (Responding to the occurrence of a fault, e.g. fault tolerance): 2 patents

- G11C16/3459 ({Circuits or methods to verify correct programming of nonvolatile memory cells}): 2 patents

- H03M13/1128 (CODING; DECODING; CODE CONVERSION IN GENERAL (using fluidic means): 2 patents

- G06F3/0653 ({Monitoring storage devices or systems}): 1 patents

- G06F3/0647 ({Migration mechanisms}): 1 patents

- G06F11/1402 ({Saving, restoring, recovering or retrying}): 1 patents

- G11C11/5642 ({Sensing or reading circuits; Data output circuits}): 1 patents

- G06F18/214 (Generating training patterns; Bootstrap methods, e.g. bagging or boosting): 1 patents

- G06N20/00 (Machine learning): 1 patents

- G11C7/02 (with means for avoiding parasitic signals): 1 patents

- G11C29/12005 (STATIC STORES (semiconductor memory devices): 1 patents

- G11C29/14 (STATIC STORES (semiconductor memory devices): 1 patents

- G11C29/38 (STATIC STORES (semiconductor memory devices): 1 patents

- G06F3/0623 ({in relation to content}): 1 patents

- G06F9/30029 ({Logical and Boolean instructions, e.g. XOR, NOT}): 1 patents

- G06F3/0625 ({Power saving in storage systems}): 1 patents

- G11C7/04 (with means for avoiding disturbances due to temperature effects): 1 patents

- G06F11/0793 ({Remedial or corrective actions (recovery from an exception in an instruction pipeline): 1 patents

- G11C16/10 (Programming or data input circuits): 1 patents

- G11C16/102 (Programming or data input circuits): 1 patents

- H03M13/611 (CODING; DECODING; CODE CONVERSION IN GENERAL (using fluidic means): 1 patents

- H03M13/098 (Error detection only, e.g. using cyclic redundancy check [CRC] codes or single parity bit): 1 patents

- H03M13/015 (CODING; DECODING; CODE CONVERSION IN GENERAL (using fluidic means): 1 patents

- G11C16/32 (Timing circuits): 1 patents

- G06F9/3001 ({Arithmetic instructions}): 1 patents

- G06F7/5443 (for evaluating functions by calculation {(): 1 patents

- G06F9/30032 ({Movement instructions, e.g. MOVE, SHIFT, ROTATE, SHUFFLE}): 1 patents

- G06F9/30043 ({LOAD or STORE instructions; Clear instruction}): 1 patents

- H03M13/2906 (CODING; DECODING; CODE CONVERSION IN GENERAL (using fluidic means): 1 patents

- H03M13/3746 (CODING; DECODING; CODE CONVERSION IN GENERAL (using fluidic means): 1 patents

- G06F11/1004 ({to protect a block of data words, e.g. CRC or checksum (): 1 patents

Companies

List of Companies

- Micron Technology, Inc.: 18 patents

- MICRON TECHNOLOGY, INC.: 5 patents

Collaborators

- Mustafa N. Kaynak of San Diego CA (US) (18 collaborations)

- Patrick R. Khayat of San Diego CA (US) (6 collaborations)

- Kishore Kumar Muchherla of San Jose CA (US) (5 collaborations)

- James Fitzpatrick of Laguna Niguel CA (US) (5 collaborations)

- Kishore Kumar Muchherla of Fremont CA (US) (4 collaborations)

- Mark A. Helm of Santa Cruz CA (US) (3 collaborations)

- Akira Goda (3 collaborations)

- Peter Feeley of Boise ID (US) (2 collaborations)

- Shane Nowell of Boise ID (US) (2 collaborations)

- Ugo Russo of Boise ID (US) (2 collaborations)

- Vamsi Pavan Rayaprolu of Santa Clara CA (US) (2 collaborations)

- Patrick Robert Khayat of San Diego CA (US) (2 collaborations)

- Steven Michael Kientz of Westminster CO (US) (2 collaborations)

- Vamsi Pavan Rayaprolu of San Jose CA (US) (2 collaborations)

- Eyal En Gad of Highland CA (US) (2 collaborations)

- Zhengang Chen of San Jose CA (US) (2 collaborations)

- Devin M. Batutis of San Jose CA (US) (1 collaborations)

- Xiangang Luo of Fremont CA (US) (1 collaborations)

- Sampath Ratnam of Boise ID (US) (1 collaborations)

- Niccolo’ Righetti of Boise ID (US) (1 collaborations)

- Sampath K. Ratnam of San Jose CA (US) (1 collaborations)

- Qisong Lin of El Dorado Hills CA (US) (1 collaborations)

- AbdelHakim S. Alhussien of San Jose CA (US) (1 collaborations)

- Jeffrey S. McNeil of Nampa ID (US) (1 collaborations)

- Sundararajan Sankaranarayanan of Fremont CA (US) (1 collaborations)

- Jeremy Binfet of Boise ID (US) (1 collaborations)

- Huai-Yuan Tseng of San Ramon CA (US) (1 collaborations)

- Jonathan Scott Parry of Boise ID (US) (1 collaborations)

- Patrick Khayat of San Diego CA (US) (1 collaborations)

- Sampath Ratnam of San Jose CA (US) (1 collaborations)

- Jiangang Wu of Milpitas CA (US) (1 collaborations)

- Jonathan S. Parry of Boise ID (US) (1 collaborations)

- Niccolo' Righetti of Boise ID (US) (1 collaborations)

- Dung Viet Nguyen of San Jose CA (US) (1 collaborations)

- Dheeraj Srinivasan of San Jose CA (US) (1 collaborations)

- Dmitri Yudanov of Cordova CA (US) (1 collaborations)

- Sean S. Eilert of Penryn CA (US) (1 collaborations)

- Shivasankar Gunasekaran of Folsom CA (US) (1 collaborations)

- Ameen D. Akel of Rancho Cordova CA (US) (1 collaborations)

Subcategories

This category has the following 4 subcategories, out of 4 total.

A

J

M

S

Pages in category "Sivagnanam Parthasarathy of Carlsbad CA (US)"

The following 40 pages are in this category, out of 40 total.

1

- 17829913. EARLY STOPPING OF BIT-FLIP LOW DENSITY PARITY CHECK DECODING BASED ON SYNDROME WEIGHT simplified abstract (Micron Technology, Inc.)

- 17829924. SCALED BIT FLIP THRESHOLDS ACROSS COLUMNS FOR IRREGULAR LOW DENSITY PARITY CHECK DECODING simplified abstract (Micron Technology, Inc.)

- 17830166. MANAGING QUAD-LEVEL CELL COMPACTION STRATEGY OF A MEMORY DEVICE simplified abstract (Micron Technology, Inc.)

- 17859468. MEMORY COMPACTION MANAGEMENT IN MEMORY DEVICES simplified abstract (Micron Technology, Inc.)

- 17860690. MANAGING COMPENSATION FOR CHARGE COUPLING AND LATERAL MIGRATION IN MEMORY DEVICES simplified abstract (Micron Technology, Inc.)

- 17860701. MANAGING ERROR COMPENSATION USING CHARGE COUPLING AND LATERAL MIGRATION SENSITIVITY simplified abstract (Micron Technology, Inc.)

- 17860711. MANAGING PROGRAM VERIFY VOLTAGE OFFSETS FOR CHARGE COUPLING AND LATERAL MIGRATION COMPENSATION IN MEMORY DEVICES simplified abstract (Micron Technology, Inc.)

- 17884107. MANAGING COMPENSATION FOR CELL-TO-CELL COUPLING AND LATERAL MIGRATION IN MEMORY DEVICES USING SEGMENTATION simplified abstract (Micron Technology, Inc.)

- 17884113. MANAGING COMPENSATION FOR CELL-TO-CELL COUPLING AND LATERAL MIGRATION IN MEMORY DEVICES BASED ON A SENSITIVITY METRIC simplified abstract (Micron Technology, Inc.)

- 17884432. MULTI-LAYER CODE RATE ARCHITECTURE FOR SPECIAL EVENT PROTECTION WITH REDUCED PERFORMANCE PENALTY simplified abstract (Micron Technology, Inc.)

- 17897869. ADJUSTMENT OF CODE RATE AS FUNCTION OF MEMORY ENDURANCE STATE METRIC simplified abstract (Micron Technology, Inc.)

- 18228291. MEMORY DEVICE PRODUCING METADATA CHARACTERIZING APPLIED READ VOLTAGE LEVEL WITH RESPECT TO VOLTAGE DISTRIBUTIONS simplified abstract (Micron Technology, Inc.)

- 18401251. USING DUPLICATE DATA FOR IMPROVING ERROR CORRECTION CAPABILITY simplified abstract (Micron Technology, Inc.)

- 18419846. DESCRAMBLING OF SCRAMBLED LINEAR CODEWORDS USING NON-LINEAR SCRAMBLERS simplified abstract (Micron Technology, Inc.)

- 18432326. MEMORY COMPACTION MANAGEMENT IN MEMORY DEVICES simplified abstract (Micron Technology, Inc.)

- 18511698. MULTI-LAYER CODE RATE ARCHITECTURE FOR COPYBACK BETWEEN PARTITIONS WITH DIFFERENT CODE RATES simplified abstract (Micron Technology, Inc.)

- 18521574. BIT FLIPPING DECODER WITH OPTIMIZED MAXIMUM ITERATIONS FOR VARIED BIT FLIPPING THRESHOLDS simplified abstract (Micron Technology, Inc.)

- 18582520. METHODS FOR PERFORMING PROCESSING-IN-MEMORY OPERATIONS, AND RELATED SYSTEMS simplified abstract (Micron Technology, Inc.)

- 18611450. ADJUSTMENT OF CODE RATE AS FUNCTION OF MEMORY ENDURANCE STATE METRIC simplified abstract (Micron Technology, Inc.)

- 18616006. VOLTAGE BIN CALIBRATION BASED ON A VOLTAGE DISTRIBUTION REFERENCE VOLTAGE simplified abstract (Micron Technology, Inc.)

- 18657672. READ DISTURB MITIGATION BASED ON SIGNAL AND NOISE CHARACTERISTICS OF MEMORY CELLS COLLECTED FOR READ CALIBRATION simplified abstract (Micron Technology, Inc.)

- 18678949. Classification of Error Rate of Data Retrieved from Memory Cells simplified abstract (Micron Technology, Inc.)

- 18743629. Separation of Parity Columns in Bit-Flip Decoding of Low-Density Parity-Check Codes with Pipelining and Column Parallelism simplified abstract (Micron Technology, Inc.)

- 18753717. MANAGING PROGRAM VERIFY VOLTAGE OFFSETS FOR CHARGE COUPLING AND LATERAL MIGRATION COMPENSATION IN MEMORY DEVICES simplified abstract (Micron Technology, Inc.)

M

- Micron technology, inc. (20240160363). DESCRAMBLING OF SCRAMBLED LINEAR CODEWORDS USING NON-LINEAR SCRAMBLERS simplified abstract

- Micron technology, inc. (20240176509). BIT FLIPPING DECODER WITH OPTIMIZED MAXIMUM ITERATIONS FOR VARIED BIT FLIPPING THRESHOLDS simplified abstract

- Micron technology, inc. (20240176698). MEMORY COMPACTION MANAGEMENT IN MEMORY DEVICES simplified abstract

- Micron technology, inc. (20240185915). OPTIMIZATION OF SOFT BIT WINDOWS BASED ON SIGNAL AND NOISE CHARACTERISTICS OF MEMORY CELLS simplified abstract

- Micron technology, inc. (20240192953). METHODS FOR PERFORMING PROCESSING-IN-MEMORY OPERATIONS, AND RELATED SYSTEMS simplified abstract

- Micron technology, inc. (20240231676). VOLTAGE BIN CALIBRATION BASED ON A VOLTAGE DISTRIBUTION REFERENCE VOLTAGE simplified abstract

- Micron technology, inc. (20240232013). ADJUSTMENT OF CODE RATE AS FUNCTION OF MEMORY ENDURANCE STATE METRIC simplified abstract

- Micron technology, inc. (20240256328). PREVENTING BACK-TO-BACK FLIPS OF A BIT IN BIT FLIPPING DECODING simplified abstract

- Micron technology, inc. (20240265979). Selective and Dynamic Deployment of Error Correction Code Techniques in Integrated Circuit Memory Devices simplified abstract

- Micron technology, inc. (20240296896). READ DISTURB MITIGATION BASED ON SIGNAL AND NOISE CHARACTERISTICS OF MEMORY CELLS COLLECTED FOR READ CALIBRATION simplified abstract

- Micron technology, inc. (20240312530). Classification of Error Rate of Data Retrieved from Memory Cells simplified abstract

- Micron technology, inc. (20240338146). Separation of Parity Columns in Bit-Flip Decoding of Low-Density Parity-Check Codes with Pipelining and Column Parallelism simplified abstract

- Micron technology, inc. (20240347119). MANAGING PROGRAM VERIFY VOLTAGE OFFSETS FOR CHARGE COUPLING AND LATERAL MIGRATION COMPENSATION IN MEMORY DEVICES simplified abstract

Categories:

- Mustafa N. Kaynak of San Diego CA (US)

- Patrick R. Khayat of San Diego CA (US)

- Kishore Kumar Muchherla of San Jose CA (US)

- James Fitzpatrick of Laguna Niguel CA (US)

- Kishore Kumar Muchherla of Fremont CA (US)

- Mark A. Helm of Santa Cruz CA (US)

- Akira Goda

- Peter Feeley of Boise ID (US)

- Shane Nowell of Boise ID (US)

- Ugo Russo of Boise ID (US)

- Vamsi Pavan Rayaprolu of Santa Clara CA (US)

- Patrick Robert Khayat of San Diego CA (US)

- Steven Michael Kientz of Westminster CO (US)

- Vamsi Pavan Rayaprolu of San Jose CA (US)

- Eyal En Gad of Highland CA (US)

- Zhengang Chen of San Jose CA (US)

- Devin M. Batutis of San Jose CA (US)

- Xiangang Luo of Fremont CA (US)

- Sampath Ratnam of Boise ID (US)

- Niccolo’ Righetti of Boise ID (US)

- Sampath K. Ratnam of San Jose CA (US)

- Qisong Lin of El Dorado Hills CA (US)

- AbdelHakim S. Alhussien of San Jose CA (US)

- Jeffrey S. McNeil of Nampa ID (US)

- Sundararajan Sankaranarayanan of Fremont CA (US)

- Jeremy Binfet of Boise ID (US)

- Huai-Yuan Tseng of San Ramon CA (US)

- Jonathan Scott Parry of Boise ID (US)

- Patrick Khayat of San Diego CA (US)

- Sampath Ratnam of San Jose CA (US)

- Jiangang Wu of Milpitas CA (US)

- Jonathan S. Parry of Boise ID (US)

- Niccolo' Righetti of Boise ID (US)

- Dung Viet Nguyen of San Jose CA (US)

- Dheeraj Srinivasan of San Jose CA (US)

- Dmitri Yudanov of Cordova CA (US)

- Sean S. Eilert of Penryn CA (US)

- Shivasankar Gunasekaran of Folsom CA (US)

- Ameen D. Akel of Rancho Cordova CA (US)

- Sivagnanam Parthasarathy of Carlsbad CA (US)

- Inventors

- Inventors filing patents with MICRON TECHNOLOGY, INC.

- Inventors filing patents with Micron Technology, Inc.