Category:Yu-Chung Lien of San Jose CA (US)

Jump to navigation

Jump to search

Contents

Yu-Chung Lien of San Jose CA (US)

Executive Summary

Yu-Chung Lien of San Jose CA (US) is an inventor who has filed 28 patents. Their primary areas of innovation include {Circuits or methods to verify correct programming of nonvolatile memory cells} (10 patents), Programming or data input circuits (9 patents), Sensing or reading circuits; Data output circuits (8 patents), and they have worked with companies such as Micron Technology, Inc. (22 patents), MICRON TECHNOLOGY, INC. (6 patents). Their most frequent collaborators include (25 collaborations), (4 collaborations), (3 collaborations).

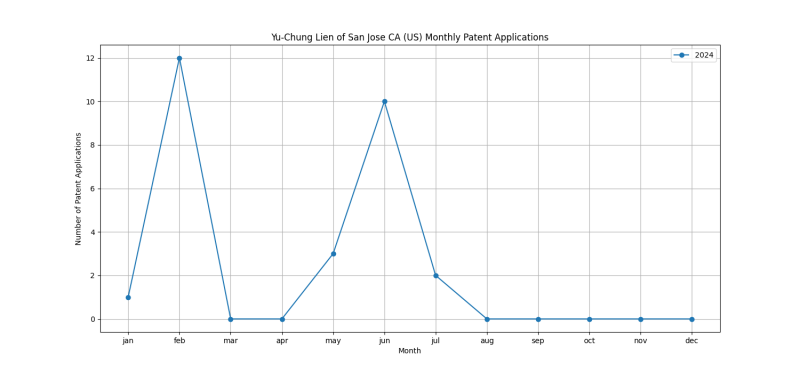

Patent Filing Activity

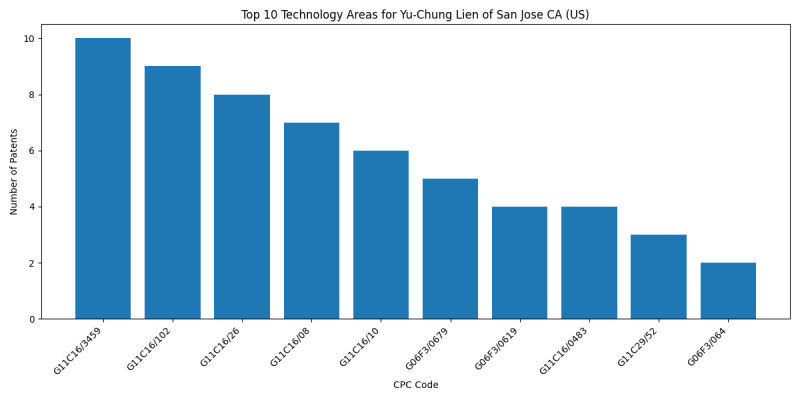

Technology Areas

List of Technology Areas

- G11C16/3459 ({Circuits or methods to verify correct programming of nonvolatile memory cells}): 10 patents

- G11C16/102 (Programming or data input circuits): 9 patents

- G11C16/26 (Sensing or reading circuits; Data output circuits): 8 patents

- G11C16/08 (Address circuits; Decoders; Word-line control circuits): 7 patents

- G11C16/10 (Programming or data input circuits): 6 patents

- G06F3/0679 ({Non-volatile semiconductor memory device, e.g. flash memory, one time programmable memory [OTP]}): 5 patents

- G06F3/0619 ({in relation to data integrity, e.g. data losses, bit errors}): 4 patents

- G11C16/0483 ({comprising cells having several storage transistors connected in series}): 4 patents

- G11C29/52 (STATIC STORES (semiconductor memory devices): 3 patents

- G06F3/064 ({Management of blocks}): 2 patents

- G11C16/30 (Power supply circuits): 2 patents

- G11C16/3404 ({Convergence or correction of memory cell threshold voltages; Repair or recovery of overerased or overprogrammed cells}): 2 patents

- G11C29/022 (STATIC STORES (semiconductor memory devices): 2 patents

- G11C16/24 (Bit-line control circuits): 2 patents

- G06F3/0653 ({Monitoring storage devices or systems}): 2 patents

- G06F3/0659 ({Command handling arrangements, e.g. command buffers, queues, command scheduling}): 2 patents

- G11C16/32 (Timing circuits): 2 patents

- G11C16/349 ({Arrangements for evaluating degradation, retention or wearout, e.g. by counting erase cycles}): 2 patents

- G06F12/1009 (Address translation): 1 patents

- G11C5/063 (STATIC STORES (semiconductor memory devices): 1 patents

- G11C16/3495 ({Arrangements for evaluating degradation, retention or wearout, e.g. by counting erase cycles}): 1 patents

- G06F3/0611 ({in relation to response time}): 1 patents

- G06F3/0616 ({in relation to life time, e.g. increasing Mean Time Between Failures [MTBF]}): 1 patents

- G11C16/12 (Programming voltage switching circuits): 1 patents

- G11C16/28 (STATIC STORES (semiconductor memory devices): 1 patents

- G06F3/0644 ({Management of space entities, e.g. partitions, extents, pools}): 1 patents

- G06F11/1068 ({in sector programmable memories, e.g. flash disk (): 1 patents

- G06F11/1489 ({through recovery blocks}): 1 patents

- G06F11/3409 ({for performance assessment}): 1 patents

- G06F11/0769 (Responding to the occurrence of a fault, e.g. fault tolerance): 1 patents

- G06F11/073 (Responding to the occurrence of a fault, e.g. fault tolerance): 1 patents

- G06F3/0673 ({Single storage device}): 1 patents

- G11C11/4096 (Input/output [I/O] data management or control circuits, e.g. reading or writing circuits, I/O drivers or bit-line switches): 1 patents

- G11C11/4074 (Power supply or voltage generation circuits, e.g. bias voltage generators, substrate voltage generators, back-up power, power control circuits): 1 patents

- G11C11/4076 (Timing circuits (for regeneration management): 1 patents

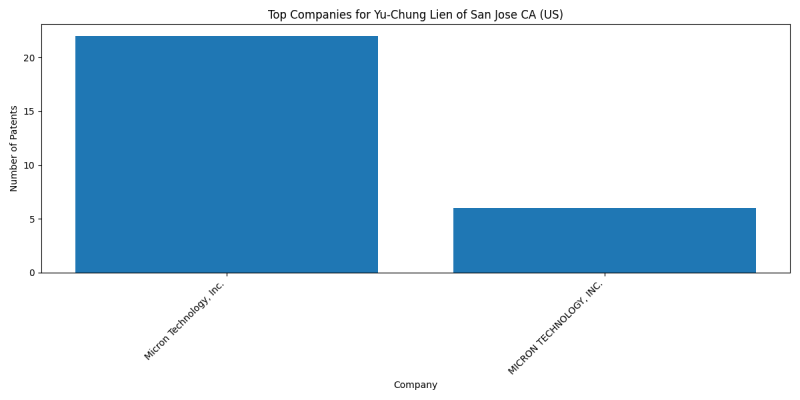

Companies

List of Companies

- Micron Technology, Inc.: 22 patents

- MICRON TECHNOLOGY, INC.: 6 patents

Collaborators

- Zhenming Zhou of San Jose CA (US) (25 collaborations)

- Tomer Tzvi Eliash of Sunnyvale CA (US) (4 collaborations)

- Jun Wan of San Jose CA (US) (3 collaborations)

- Murong Lang of San Jose CA (US) (3 collaborations)

- Ching-Huang Lu of Fremont CA (US) (3 collaborations)

- Christina Papagianni of San Jose CA (US) (1 collaborations)

- Zhengang Chen of San Jose CA (US) (1 collaborations)

- Jameer Mulani (1 collaborations)

- Vivek Shivhare of Milpitas CA (US) (1 collaborations)

- Vinh Diep of Hayward CA (US) (1 collaborations)

- Zhongguang Xu of San Jose CA (US) (1 collaborations)

- Ronit Roneel Prakash (1 collaborations)

- Joshua Garrison of Folsom CA (US) (1 collaborations)

- Wei Wang of Fremont CA (US) (1 collaborations)

- Li-Te Chang of San Jose CA (US) (1 collaborations)

- Michael G. Miller of Boise ID (US) (1 collaborations)

- Ankit V. Vashi of San Jose CA (US) (1 collaborations)

- Jung Sheng Hoei of Newark CA (US) (1 collaborations)

Subcategories

This category has the following 3 subcategories, out of 3 total.

M

Y

Z

Pages in category "Yu-Chung Lien of San Jose CA (US)"

The following 45 pages are in this category, out of 45 total.

1

- 17819826. DETECTING A MEMORY WRITE RELIABILITY RISK WITHOUT USING A WRITE VERIFY OPERATION simplified abstract (Micron Technology, Inc.)

- 17830802. DYNAMIC READ LEVEL TRIM SELECTION FOR SCAN OPERATIONS OF MEMORY DEVICES simplified abstract (Micron Technology, Inc.)

- 17874828. RELIABILITY BASED DATA VERIFICATION simplified abstract (Micron Technology, Inc.)

- 17887348. INDEPENDENT SENSING TIMES simplified abstract (Micron Technology, Inc.)

- 17888080. ADAPTIVE BITLINE VOLTAGE FOR MEMORY OPERATIONS simplified abstract (Micron Technology, Inc.)

- 17888171. ADAPTIVE SENSING TIME FOR MEMORY OPERATIONS simplified abstract (Micron Technology, Inc.)

- 17888225. ADAPTIVE SENSING TIME FOR MEMORY OPERATIONS simplified abstract (Micron Technology, Inc.)

- 17894528. ADAPTIVE ERROR AVOIDANCE IN THE MEMORY DEVICES simplified abstract (Micron Technology, Inc.)

- 17897183. PROXIMITY BASED PARITY DATA MANAGEMENT simplified abstract (Micron Technology, Inc.)

- 17897184. PADDING IN FLASH MEMORY BLOCKS simplified abstract (Micron Technology, Inc.)

- 18388506. READ OPERATION WITH CAPACITY USAGE DETECTION SCHEME simplified abstract (Micron Technology, Inc.)

- 18402306. MANAGING ALLOCATION OF SUB-BLOCKS IN A MEMORY SUB-SYSTEM simplified abstract (Micron Technology, Inc.)

- 18405049. ELONGATED CAPACITORS IN 3D NAND MEMORY DEVICES simplified abstract (Micron Technology, Inc.)

- 18406687. DYNAMIC READ RETRY VOLTAGE SEQUENCES IN A MEMORY SUBSYSTEM simplified abstract (Micron Technology, Inc.)

- 18439318. DYNAMIC ERASE OPERATION SELECTION USING ERASE POLICY simplified abstract (Micron Technology, Inc.)

- 18521458. RELIABILITY GAIN IN MEMORY DEVICES WITH ADAPTIVELY SELECTED ERASE POLICIES simplified abstract (Micron Technology, Inc.)

- 18524721. MANAGING ASYNCHRONOUS POWER LOSS IN A MEMORY DEVICE simplified abstract (Micron Technology, Inc.)

- 18663978. ADAPTIVE SENSING TIME FOR MEMORY OPERATIONS simplified abstract (Micron Technology, Inc.)

- 18666063. PROGRAMMING DELAY SCHEME FOR IN A MEMORY SUB-SYSTEM BASED ON MEMORY RELIABILITY simplified abstract (Micron Technology, Inc.)

- 18820480. DETECTING A MEMORY WRITE RELIABILITY RISK WITHOUT USING A WRITE VERIFY OPERATION (Micron Technology, Inc.)

- 18821484. PROXIMITY BASED PARITY DATA MANAGEMENT (Micron Technology, Inc.)

M

- Micron technology, inc. (20240176508). RELIABILITY GAIN IN MEMORY DEVICES WITH ADAPTIVELY SELECTED ERASE POLICIES simplified abstract

- Micron technology, inc. (20240177781). READ OPERATION WITH CAPACITY USAGE DETECTION SCHEME simplified abstract

- Micron technology, inc. (20240185924). PASS VOLTAGE ADJUSTMENT FOR PROGRAM OPERATION IN A MEMORY DEVICE WITH A DEFECTIVE DECK simplified abstract

- Micron technology, inc. (20240185931). PROGRAM VERIFY COMPENSATION IN A MEMORY DEVICE WITH A DEFECTIVE DECK simplified abstract

- Micron technology, inc. (20240185934). PROGRAM VERIFY COMPENSATION BY SENSING TIME MODULATION IN A MEMORY DEVICE WITH A DEFECTIVE DECK simplified abstract

- Micron technology, inc. (20240185935). BITLINE VOLTAGE ADJUSTMENT FOR PROGRAM OPERATION IN A MEMORY DEVICE WITH A DEFECTIVE DECK simplified abstract

- Micron technology, inc. (20240194279). MANAGING ASYNCHRONOUS POWER LOSS IN A MEMORY DEVICE simplified abstract

- Micron technology, inc. (20240203502). BITLINE VOLTAGE ADJUSTMENT FOR PROGRAM OPERATION IN A MEMORY DEVICE simplified abstract

- Micron technology, inc. (20240203503). PROGRAM VERIFY LEVEL ADJUSTMENT FOR PROGRAM OPERATION IN A MEMORY DEVICE simplified abstract

- Micron technology, inc. (20240203504). SENSING TIME ADJUSTMENT FOR PROGRAM OPERATION IN A MEMORY DEVICE simplified abstract

- Micron technology, inc. (20240203507). MANAGING ALLOCATION OF BLOCKS IN A MEMORY SUB-SYSTEM simplified abstract

- Micron technology, inc. (20240203513). PASS VOLTAGE ADJUSTMENT FOR PROGRAM OPERATION IN A MEMORY DEVICE simplified abstract

- Micron technology, inc. (20240231641). MANAGING ALLOCATION OF SUB-BLOCKS IN A MEMORY SUB-SYSTEM simplified abstract

- Micron technology, inc. (20240248619). DYNAMIC READ RETRY VOLTAGE SEQUENCES IN A MEMORY SUBSYSTEM simplified abstract

- Micron technology, inc. (20240249772). ELONGATED CAPACITORS IN 3D NAND MEMORY DEVICES simplified abstract

- Micron technology, inc. (20240256155). MEMORY READ OPERATION USING A VOLTAGE PATTERN BASED ON A READ COMMAND TYPE simplified abstract

- Micron technology, inc. (20240281145). DYNAMIC ERASE OPERATION SELECTION USING ERASE POLICY simplified abstract

- Micron technology, inc. (20240302967). ADAPTIVE SENSING TIME FOR MEMORY OPERATIONS simplified abstract

- Micron technology, inc. (20240304256). PROGRAMMING DELAY SCHEME FOR IN A MEMORY SUB-SYSTEM BASED ON MEMORY RELIABILITY simplified abstract

- Micron technology, inc. (20240411449). MANAGING PROGRAMMING OPERATION SEQUENCE IN A MEMORY SUB-SYSTEM

- Micron technology, inc. (20240419543). PROXIMITY BASED PARITY DATA MANAGEMENT

- Micron technology, inc. (20240420783). DETECTING A MEMORY WRITE RELIABILITY RISK WITHOUT USING A WRITE VERIFY OPERATION

Categories:

- Zhenming Zhou of San Jose CA (US)

- Tomer Tzvi Eliash of Sunnyvale CA (US)

- Jun Wan of San Jose CA (US)

- Murong Lang of San Jose CA (US)

- Ching-Huang Lu of Fremont CA (US)

- Christina Papagianni of San Jose CA (US)

- Zhengang Chen of San Jose CA (US)

- Jameer Mulani

- Vivek Shivhare of Milpitas CA (US)

- Vinh Diep of Hayward CA (US)

- Zhongguang Xu of San Jose CA (US)

- Ronit Roneel Prakash

- Joshua Garrison of Folsom CA (US)

- Wei Wang of Fremont CA (US)

- Li-Te Chang of San Jose CA (US)

- Michael G. Miller of Boise ID (US)

- Ankit V. Vashi of San Jose CA (US)

- Jung Sheng Hoei of Newark CA (US)

- Yu-Chung Lien of San Jose CA (US)

- Inventors

- Inventors filing patents with Micron Technology, Inc.

- Inventors filing patents with MICRON TECHNOLOGY, INC.