Category:Ruilong Xie of Niskayuna NY (US)

Contents

Ruilong Xie of Niskayuna NY (US)

Executive Summary

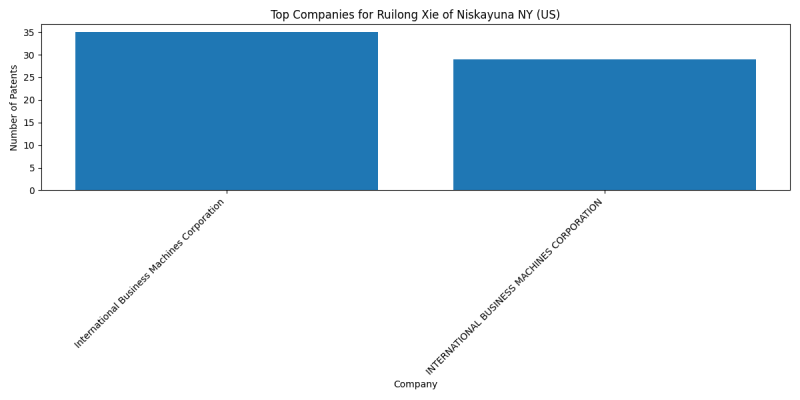

Ruilong Xie of Niskayuna NY (US) is an inventor who has filed 64 patents. Their primary areas of innovation include SEMICONDUCTOR DEVICES NOT COVERED BY CLASS (22 patents), SEMICONDUCTOR DEVICES NOT COVERED BY CLASS (22 patents), SEMICONDUCTOR DEVICES NOT COVERED BY CLASS (21 patents), and they have worked with companies such as International Business Machines Corporation (35 patents), INTERNATIONAL BUSINESS MACHINES CORPORATION (29 patents). Their most frequent collaborators include (20 collaborations), (18 collaborations), (14 collaborations).

Patent Filing Activity

Technology Areas

List of Technology Areas

- H01L29/42392 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 22 patents

- H01L29/775 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 22 patents

- H01L29/0673 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 21 patents

- H10D30/6735 (No explanation available): 21 patents

- H10D62/121 (No explanation available): 20 patents

- H10D30/43 (No explanation available): 19 patents

- H10D30/6757 (No explanation available): 16 patents

- H01L29/78696 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 14 patents

- H01L29/66439 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 14 patents

- H10D30/014 (No explanation available): 14 patents

- H01L27/088 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 13 patents

- H01L29/66545 ({using a dummy, i.e. replacement gate in a process wherein at least a part of the final gate is self aligned to the dummy gate}): 11 patents

- H01L23/5286 ({Geometry or} layout of the interconnection structure {(): 11 patents

- H01L23/5226 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 10 patents

- H01L23/481 (Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements {; Selection of materials therefor}): 10 patents

- H10D84/038 (No explanation available): 10 patents

- H10D30/6729 (No explanation available): 9 patents

- H10D84/83 (No explanation available): 9 patents

- H10D64/017 (No explanation available): 8 patents

- H01L21/823475 (to produce devices, e.g. integrated circuits, each consisting of a plurality of components): 7 patents

- H01L21/823807 (to produce devices, e.g. integrated circuits, each consisting of a plurality of components): 5 patents

- H01L27/092 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 5 patents

- H01L21/823481 (to produce devices, e.g. integrated circuits, each consisting of a plurality of components): 5 patents

- H10D62/151 (No explanation available): 5 patents

- H10D84/85 (No explanation available): 5 patents

- H01L23/5283 ({Geometry or} layout of the interconnection structure {(): 4 patents

- H01L29/41733 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 4 patents

- H01L21/823418 (to produce devices, e.g. integrated circuits, each consisting of a plurality of components): 4 patents

- H01L29/0847 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 4 patents

- H01L29/41766 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 4 patents

- H10D84/013 (No explanation available): 4 patents

- H10D84/017 (No explanation available): 4 patents

- H01L21/823412 (to produce devices, e.g. integrated circuits, each consisting of a plurality of components): 3 patents

- H01L27/124 (the substrate being other than a semiconductor body, e.g. an insulating body): 3 patents

- H01L27/1266 (the substrate being other than a semiconductor body, e.g. an insulating body): 3 patents

- H01L23/564 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 3 patents

- H01L23/585 ({comprising conductive layers or plates or strips or rods or rings (): 3 patents

- H01L23/60 (Protection against electrostatic charges or discharges, e.g. Faraday shields): 3 patents

- H01L21/76897 ({Formation of self-aligned vias or contact plugs, i.e. involving a lithographically uncritical step (self-aligned silicidation on field effect transistors): 3 patents

- H10D84/0149 (No explanation available): 3 patents

- H10D84/0128 (No explanation available): 3 patents

- H10D64/258 (No explanation available): 3 patents

- H10B10/125 (ELECTRONIC MEMORY DEVICES): 2 patents

- H01L29/41725 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L21/823468 (to produce devices, e.g. integrated circuits, each consisting of a plurality of components): 2 patents

- H01L29/6656 ({using self aligned silicidation, i.e. salicide (formation of conductive layers comprising silicides): 2 patents

- H01L27/0922 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L21/8221 ({Three dimensional integrated circuits stacked in different levels}): 2 patents

- H01L21/76804 ({by forming tapered via holes}): 2 patents

- H01L21/76898 ({formed through a semiconductor substrate}): 2 patents

- H01L23/528 ({Geometry or} layout of the interconnection structure {(): 2 patents

- H01L25/0657 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L2225/06541 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L23/562 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H10B10/12 (ELECTRONIC MEMORY DEVICES): 2 patents

- H01L21/823871 (to produce devices, e.g. integrated circuits, each consisting of a plurality of components): 2 patents

- H01L21/76224 ({using trench refilling with dielectric materials (trench filling with polycristalline silicon): 2 patents

- H01L29/401 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L27/0928 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H10D30/024 (No explanation available): 2 patents

- H10D62/154 (No explanation available): 2 patents

- H10D62/158 (No explanation available): 2 patents

- H10D84/811 (No explanation available): 2 patents

- H10D84/0186 (No explanation available): 2 patents

- H01L23/5256 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H10D64/256 (No explanation available): 2 patents

- H10D64/021 (No explanation available): 2 patents

- H10D64/01 (No explanation available): 2 patents

- H01L21/76886 ({Modifying permanently or temporarily the pattern or the conductivity of conductive members, e.g. formation of alloys, reduction of contact resistances}): 1 patents

- H01L21/28123 ({Lithography-related aspects, e.g. sub-lithography lengths; Isolation-related aspects, e.g. to solve problems arising at the crossing with the side of the device isolation; Planarisation aspects}): 1 patents

- H01L27/1207 ({combined with devices in contact with the semiconductor body, i.e. bulk/SOI hybrid circuits}): 1 patents

- H01L21/823462 (to produce devices, e.g. integrated circuits, each consisting of a plurality of components): 1 patents

- H01L21/84 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L24/16 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2224/16227 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2924/14 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L23/5223 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L21/768 (Applying interconnections to be used for carrying current between separate components within a device {comprising conductors and dielectrics}): 1 patents

- H01L24/05 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L24/08 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2224/08145 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2924/19041 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L29/0649 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L29/66977 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L21/823885 ({with a particular manufacturing method of vertical transistor structures, i.e. with channel vertical to the substrate surface (with a current flow parallel to the substrate surface): 1 patents

- H01L29/66666 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L29/7827 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L21/76802 (Applying interconnections to be used for carrying current between separate components within a device {comprising conductors and dielectrics}): 1 patents

- H01L21/76831 ({in via holes or trenches, e.g. non-conductive sidewall liners}): 1 patents

- H01L21/76885 ({By forming conductive members before deposition of protective insulating material, e.g. pillars, studs}): 1 patents

- H01L27/0924 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L21/823842 (to produce devices, e.g. integrated circuits, each consisting of a plurality of components): 1 patents

- H01L21/823437 (to produce devices, e.g. integrated circuits, each consisting of a plurality of components): 1 patents

- H01L21/76816 ({Aspects relating to the layout of the pattern or to the size of vias or trenches (layout of the interconnections per se): 1 patents

- H01L21/823864 (to produce devices, e.g. integrated circuits, each consisting of a plurality of components): 1 patents

- H01L29/66553 ({using self aligned silicidation, i.e. salicide (formation of conductive layers comprising silicides): 1 patents

- H01L29/0653 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L23/66 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L23/49822 ({Multilayer substrates (multilayer metallisation on monolayer substrate): 1 patents

- H01Q1/2283 ({mounted in or on the surface of a semiconductor substrate as a chip-type antenna or integrated with other components into an IC package}): 1 patents

- H01Q1/50 (Structural association of antennas with earthing switches, lead-in devices or lightning protectors): 1 patents

- H10D8/00 (No explanation available): 1 patents

- H01L2223/6616 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2223/6677 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H10D30/6748 (No explanation available): 1 patents

- H01L21/308 (using masks (): 1 patents

- H01L27/1255 (the substrate being other than a semiconductor body, e.g. an insulating body): 1 patents

- H01L27/127 (the substrate being other than a semiconductor body, e.g. an insulating body): 1 patents

- H01L21/76229 (Dielectric regions {, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers}): 1 patents

- H01L21/76805 ({the opening being a via or contact hole penetrating the underlying conductor}): 1 patents

- H01L23/62 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H10D64/251 (No explanation available): 1 patents

- H01L21/7682 (Applying interconnections to be used for carrying current between separate components within a device {comprising conductors and dielectrics}): 1 patents

- H01L21/76838 ({characterised by the formation and the after-treatment of the conductors (etching for patterning the conductors): 1 patents

- H10D84/0179 (No explanation available): 1 patents

- H10D30/792 (No explanation available): 1 patents

- H10D64/018 (No explanation available): 1 patents

- H01L21/02532 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L21/02609 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L23/5228 ({Resistive arrangements or effects of, or between, wiring layers (other resistive arrangements): 1 patents

- H10D1/474 (No explanation available): 1 patents

- H10D86/80 (No explanation available): 1 patents

- H10D86/01 (No explanation available): 1 patents

- H10D86/0214 (No explanation available): 1 patents

- H10D86/481 (No explanation available): 1 patents

- H10D86/60 (No explanation available): 1 patents

- H10D87/00 (No explanation available): 1 patents

- H10D86/421 (No explanation available): 1 patents

- H01L29/41775 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L29/0669 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L23/535 (including internal interconnections, e.g. cross-under constructions {(internal lead connections): 1 patents

- H10D84/0167 (No explanation available): 1 patents

- H10D84/856 (No explanation available): 1 patents

- H10D88/01 (No explanation available): 1 patents

- G11C11/412 (using field-effect transistors only): 1 patents

- H10D84/853 (No explanation available): 1 patents

- H10D30/62 (No explanation available): 1 patents

- H10D84/0151 (No explanation available): 1 patents

- H10D84/0158 (No explanation available): 1 patents

- H10D84/834 (No explanation available): 1 patents

- H10B80/00 (Assemblies of multiple devices comprising at least one memory device covered by this subclass): 1 patents

Companies

List of Companies

- International Business Machines Corporation: 35 patents

- INTERNATIONAL BUSINESS MACHINES CORPORATION: 29 patents

Collaborators

- Tao Li of Slingerlands NY (US) (20 collaborations)

- Brent A. Anderson of Jericho VT (US) (18 collaborations)

- Julien Frougier of Albany NY (US) (14 collaborations)

- Lawrence A. Clevenger of Saratoga Springs NY (US) (14 collaborations)

- Albert M. Chu of Nashua NH (US) (12 collaborations)

- Nicholas Anthony Lanzillo of Wynantskill NY (US) (10 collaborations)

- Min Gyu Sung of Latham NY (US) (10 collaborations)

- Kisik Choi of Watervliet NY (US) (9 collaborations)

- Junli Wang of Slingerlands NY (US) (8 collaborations)

- Juntao Li of Cohoes NY (US) (7 collaborations)

- Tsung-Sheng Kang of Ballston Lake NY (US) (7 collaborations)

- Tenko Yamashita of Schenectady NY (US) (6 collaborations)

- Chanro Park of Clifton Park NY (US) (6 collaborations)

- Shay Reboh of Guilderland NY (US) (5 collaborations)

- Shahrukh Khan of Sandy Hook CT (US) (5 collaborations)

- LEI ZHUANG of Ridgefield CT (US) (5 collaborations)

- Nicolas Jean Loubet of GUILDERLAND NY (US) (5 collaborations)

- Koichi Motoyama of Clifton Park NY (US) (4 collaborations)

- Jay William Strane of Wappingers Falls NY (US) (4 collaborations)

- James P. Mazza of Saratoga Springs NY (US) (4 collaborations)

- Nicholas Alexander POLOMOFF of Hopewell Junction NY (US) (4 collaborations)

- Matthew Stephen Angyal of Stormville NY (US) (4 collaborations)

- Terence Hook of Jericho Center VT (US) (4 collaborations)

- Reinaldo Vega of Mahopac NY (US) (4 collaborations)

- HUIMEI ZHOU of Albany NY (US) (3 collaborations)

- FEE LI LIE of Albany NY (US) (3 collaborations)

- John Christopher Arnold of North Chatham NY (US) (3 collaborations)

- Chen Zhang of Santa Clara CA (US) (3 collaborations)

- Lijuan Zou of Slingerlands NY (US) (3 collaborations)

- Jingyun Zhang of Albany NY (US) (3 collaborations)

- Biswanath Senapati of Mechanicville NY (US) (3 collaborations)

- JENS HAETTY of Halfmoon NY (US) (3 collaborations)

- Christopher Murphy of Red Hook NY (US) (3 collaborations)

- Chih-Chao Yang of Glenmont NY (US) (2 collaborations)

- Iqbal Rashid Saraf of Glenmont NY (US) (2 collaborations)

- Liqiao Qin of Albany NY (US) (2 collaborations)

- Nicholas Alexander Polomoff of Hopewell Junction NY (US) (2 collaborations)

- Huimei Zhou of Albany NY (US) (2 collaborations)

- Terence B. Hook of Jericho Center VT (US) (2 collaborations)

- Dan Moy of Bethel CT (US) (2 collaborations)

- Nicolas Jean Loubet of Guilderland NY (US) (2 collaborations)

- Sagarika Mukesh of Albany NY (US) (2 collaborations)

- Alexander Reznicek of Troy NY (US) (2 collaborations)

- Leon Sigal of Monsey NY (US) (1 collaborations)

- Biswanath Senapati of Albany NY (US) (1 collaborations)

- FEE LI LIE of ALBANY NY (US) (1 collaborations)

- Jay William Strane of Wappinger Falls NY (US) (1 collaborations)

- Indira Seshadri of Niskayuna NY (US) (1 collaborations)

- FENG LIU of Niskayuna NY (US) (1 collaborations)

- Dureseti Chidambarrao of Weston CT (US) (1 collaborations)

- Ravikumar Ramachandran of Pleasantville NY (US) (1 collaborations)

- Anthony I. Chou of Guilderland NY (US) (1 collaborations)

- Albert M Chu of Nashua NH (US) (1 collaborations)

- Xiaoming Yang of Clifton Park NY (US) (1 collaborations)

- Huai Huang of Clifton Park NY (US) (1 collaborations)

- Hosadurga Shobha of Niskayuna NY (US) (1 collaborations)

- Atharv Jog of Albany NY (US) (1 collaborations)

- Susan Ng Emans of Albany NY (US) (1 collaborations)

- Miaomiao Wang of Albany NY (US) (1 collaborations)

- Baozhen Li of South Burlington VT (US) (1 collaborations)

- Yoo-Mi Lee of Montvale NJ (US) (1 collaborations)

- Utkarsh Bajpai of Delmar NY (US) (1 collaborations)

- Joshua M. Rubin of Albany NY (US) (1 collaborations)

- Shay Reboh of Albany NY (US) (1 collaborations)

- Takashi Ando of Eastchester NY (US) (1 collaborations)

- David Wolpert of Poughkeepsie NY (US) (1 collaborations)

- Julien Frougier of Frougier NY (US) (1 collaborations)

- Shogo Mochizuki of Mechanicville NY (US) (1 collaborations)

Subcategories

This category has the following 8 subcategories, out of 8 total.

A

B

C

J

L

N

R

T

Pages in category "Ruilong Xie of Niskayuna NY (US)"

The following 200 pages are in this category, out of 497 total.

(previous page) (next page)1

- 17450121. VERTICAL FET WITH CONTACT TO GATE ABOVE ACTIVE FIN simplified abstract (International Business Machines Corporation)

- 17453882. GATE-ALL-AROUND NANOSHEET-FET WITH VARIABLE CHANNEL GEOMETRIES FOR PERFORMANCE OPTIMIZATION simplified abstract (International Business Machines Corporation)

- 17455935. PARASITIC CAPACITANCE REDUCTION FOR TALL NANOSHEET DEVICES simplified abstract (International Business Machines Corporation)

- 17455937. REDUCED PARASITIC RESISTANCE TWO-DIMENSIONAL MATERIAL FIELD-EFFECT TRANSISTOR simplified abstract (International Business Machines Corporation)

- 17455941. STACKED NANOSHEET DEVICES WITH MATCHED THRESHOLD VOLTAGES FOR NFET/PFET simplified abstract (International Business Machines Corporation)

- 17457271. INTEGRATION OF HORIZONTAL NANOSHEET DEVICE AND VERTICAL NANO FINS simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17457444. TOP VIA WITH PROTECTIVE LINER simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17457448. NANOSHEET EPITAXY WITH FULL BOTTOM ISOLATION simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17457565. TOP ELECTRODE TO METAL LINE CONNECTION FOR MAGNETO-RESISTIVE RANDOM-ACCESS MEMORY STACK HEIGHT REDUCTION simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17457634. CHANNEL PROTECTION OF GATE-ALL-AROUND DEVICES FOR PERFORMANCE OPTIMIZATION simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17457667. HIGH-DENSITY METAL-INSULATOR-METAL CAPACITOR INTEGRATION WTH NANOSHEET STACK TECHNOLOGY simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17457686. METHOD TO RELEASE NANO SHEET AFTER NANO SHEET FIN RECESS simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17487301. LATE REPLACEMENT BOTTOM ISOLATION FOR NANOSHEET DEVICES simplified abstract (International Business Machines Corporation)

- 17494101. STACKED COMPLEMENTARY FIELD EFFECT TRANSISTORS simplified abstract (International Business Machines Corporation)

- 17520690. SEMICONDUCTOR DEVICE WITH BOTTOM DIELECTRIC ISOLATION simplified abstract (International Business Machines Corporation)

- 17522974. GATE-CUT AND SEPARATION TECHNIQUES FOR ENABLING INDEPENDENT GATE CONTROL OF STACKED TRANSISTORS simplified abstract (International Business Machines Corporation)

- 17524541. GATE CUT SUBSEQUENT TO REPLACEMENT GATE simplified abstract (International Business Machines Corporation)

- 17524851. SHORT GATE ON ACTIVE AND LONGER GATE ON STI FOR NANOSHEETS simplified abstract (International Business Machines Corporation)

- 17527229. REPLACEMENT BURIED POWER RAIL simplified abstract (International Business Machines Corporation)

- 17528279. TUNNEL FIELD EFFECT TRANSISTOR DEVICES simplified abstract (International Business Machines Corporation)

- 17528391. VARACTOR INTEGRATED WITH COMPLEMENTARY METAL-OXIDE SEMICONDUCTOR DEVICES simplified abstract (International Business Machines Corporation)

- 17528858. BOTTOM DIELECTRIC ISOLATION INTEGRATION WITH BURIED POWER RAIL simplified abstract (International Business Machines Corporation)

- 17531837. BURIED POWER RAIL AFTER REPLACEMENT METAL GATE simplified abstract (International Business Machines Corporation)

- 17531966. NON-SELF-ALIGNED WRAP-AROUND CONTACT IN A TIGHT GATE PITCHED TRANSISTOR simplified abstract (International Business Machines Corporation)

- 17534629. Reliability Macros for Contact Over Active Gate Layout Designs simplified abstract (International Business Machines Corporation)

- 17541529. Fork Sheet with Reduced Coupling Effect simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17542662. SELECTIVE DIPOLE LAYER MODULATION USING TWO-STEP INNER SPACER simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17543028. GATE-ALL-AROUND MONOLITHIC STACKED FIELD EFFECT TRANSISTORS HAVING MULTIPLE THRESHOLD VOLTAGES simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17543215. COMPLEMENTARY FIELD EFFECT TRANSISTORS HAVING MULTIPLE VOLTAGE THRESHOLDS simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17544328. WRAPAROUND CONTACT WITH REDUCED DISTANCE TO CHANNEL simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17545013. INTEGRATING GATE-CUTS AND SINGLE DIFFUSION BREAK ISOLATION POST-RMG USING LOW-TEMPERATURE PROTECTIVE LINERS simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17545073. BURIED POWER RAIL AT TIGHT CELL-TO-CELL SPACE simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17545074. Contact and Isolation in Monolithically Stacked VTFET simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17545485. MAGNETIC TUNNEL JUNCTION PILLAR FORMATION FOR MRAM DEVICE simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17545501. CO-INTEGRATED LOGIC, ELECTROSTATIC DISCHARGE, AND WELL CONTACT DEVICES ON A SUBSTRATE simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17545610. STACKED FETS WITH NON-SHARED WORK FUNCTION METALS simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17545635. STACKED CROSS-POINT PHASE CHANGE MEMORY simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17545713. NANOSHEET DEVICE WITH AIR-GAPED SOURCE/DRAIN REGIONS simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17548751. CO-INTEGRATING GATE-ALL-AROUND NANOSHEET TRANSISTORS AND COMB NANOSHEET TRANSISTORS simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17548913. NANOSHEET DEVICE WITH VERTICAL BLOCKER FIN simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17550658. GATE-ALL-AROUND FIELD-EFFECT-TRANSISTOR WITH WRAP-AROUND-CHANNEL INNER SPACER simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17550724. SEMICONDUCTOR STRUCTURES WITH WRAP-AROUND CONTACT STRUCTURE simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17551402. FORMING NS GATES WITH IMPROVED MECHANICAL STABILITY simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17551463. NANOSHEET DEVICE WITH T-SHAPED DUAL INNER SPACER simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17551829. ANGLED VIA FOR TIP TO TIP MARGIN IMPROVEMENT simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17643202. LINER-LESS VIA CONTACT simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17643395. ADVANCED METAL INTERCONNECT simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17644100. SELECTIVE GATE CAP FOR SELF-ALIGNED CONTACTS simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17644528. CROSS BAR VERTICAL FETS simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17806280. VIA CONNECTION TO BACKSIDE POWER DELIVERY NETWORK simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17806292. STACKED FIELD EFFECT TRANSISTOR simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17806514. SQUARE-SHAPED CONTACT WITH IMPROVED ELECTRICAL CONDUCTIVITY simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17806602. HYBRID SIGNAL AND POWER TRACK FOR STACKED TRANSISTORS simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17808116. POWER PLANES AND PASS-THROUGH VIAS simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17808124. SUBTRACTIVE SOURCE DRAIN CONTACT FOR STACKED DEVICES simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17808186. SEMICONDUCTOR DEVICE WITH POWER VIA simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17808316. INTERCONNECT WITH TWO-DIMENSIONAL FREE ZERO LINE END ENCLOSURE simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17808360. SINGLE STACK DUAL CHANNEL GATE-ALL-AROUND NANOSHEET WITH STRAINED PFET AND BOTTOM DIELECTRIC ISOLATION NFET simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17808568. CONTACTS FOR STACKED FIELD EFFECT TRANSISTOR simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17809076. STACKED FIELD EFFECT TRANSISTOR CELL WITH CROSS-COUPLING simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17837150. UNIFORM SEMICONDUCTOR ACTIVE FIN WIDTH simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17837434. SKIP-LEVEL TSV WITH HYBRID DIELECTRIC SCHEME FOR BACKSIDE POWER DELIVERY simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17849639. FORMING A FORKSHEET NANODEVICE simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17850475. CPP-AGNOSTIC SOURCE-DRAIN CONTACT FORMATION FOR GATE-ALL-AROUND DEVICES WITH DIELECTRIC ISOLATION simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17896278. Barrier-Less Jumper Structure for Line-to-Line Connections simplified abstract (International Business Machines Corporation)

- 17899111. BACKSIDE CONTACTS FOR CELL HEIGHT SCALING simplified abstract (International Business Machines Corporation)

- 17930739. GAA DEVICE WITH THE SUBSTRATE INCLUDING EMBEDDED INSULATING STRUCTURE BETWEEN BSPDN AND CHANNELS simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17931145. A SINGLE BACKSIDE POWER PLANE FOR IMPROVED POWER DELIVERY simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17931319. DIFFERENT DIMENSIONS ACROSS ACTIVE REGION FOR STRONGER VIA TO BACKSIDE POWER RAIL simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17931767. INTEGRATED CIRCUIT CHIP WITH BACKSIDE POWER DELIVERY AND MULTIPLE TYPES OF BACKSIDE TO FRONTSIDE VIAS simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17932347. VERTICAL NAND WITH BACKSIDE STACKING simplified abstract (International Business Machines Corporation)

- 17932557. HETEROGENEOUS GATE ALL AROUND DIELECTRIC THICKNESS simplified abstract (International Business Machines Corporation)

- 17932677. DUAL DIELECTRIC STRESSORS simplified abstract (International Business Machines Corporation)

- 17932679. BACKSIDE CMOS TRENCH EPI WITH CLOSE N2P SPACE simplified abstract (International Business Machines Corporation)

- 17932919. SEMICONDUCTOR BACKSIDE CONTACT STRUCTURE WITH INCREASED CONTACT AREA simplified abstract (International Business Machines Corporation)

- 17933861. SELF-ALIGNED BACKSIDE CONTACT WITH DEEP TRENCH LAST FLOW simplified abstract (International Business Machines Corporation)

- 17934195. SUBTRACTIVES LINES AND VIAS WITH WRAP-AROUND CONTACT simplified abstract (International Business Machines Corporation)

- 17936393. VERTICAL-TRANSPORT FIELD-EFFECT TRANSISTORS WITH SHARED BACKSIDE POWER SUPPLY simplified abstract (International Business Machines Corporation)

- 17936416. VERTICAL INVERTER FORMATION ON STACKED FIELD EFFECT TRANSISTOR (SFET) simplified abstract (International Business Machines Corporation)

- 17936417. MONOLITHIC STACKED FIELD EFFECT TRANSISTOR (SFET) WITH DUAL MIDDLE DIELECTRIC ISOLATION (MDI) SEPARATION simplified abstract (International Business Machines Corporation)

- 17936434. VERTICAL-TRANSPORT FIELD-EFFECT TRANSISTOR WITH BACKSIDE SOURCE/DRAIN CONNECTIONS simplified abstract (International Business Machines Corporation)

- 17936825. METHOD AND STRUCTURE OF FORMING BACKSIDE GATE TIE-DOWN simplified abstract (International Business Machines Corporation)

- 17937431. POWER GATING DUMMY POWER TRANSISTORS FOR BACK SIDE POWER DELIVERY NETWORKS simplified abstract (International Business Machines Corporation)

- 17937955. FIELD EFFECT TRANSISTOR WITH BACKSIDE SOURCE/DRAIN simplified abstract (International Business Machines Corporation)

- 17937967. FIELD EFFECT TRANSISTOR WITH BACKSIDE SOURCE/DRAIN simplified abstract (International Business Machines Corporation)

- 17938667. MULTI-STATE FERROELECTRIC-RAM WITH STACKED CAPACITORS simplified abstract (International Business Machines Corporation)

- 17941248. CONTACT JUMPER FOR NON-SELF ALIGNED CONTACT DEVICES simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17943602. BACKSIDE CONTACT WITH FULL WRAP-AROUND CONTACT simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17943751. HEIGHT CONTROL IN NANOSHEET DEVICES simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17943799. LINE EXTENSION FOR SKIP-LEVEL VIA LANDING simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17944437. BACKSIDE CONTACT WITH FULL WRAP-AROUND CONTACT simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17945418. SELF-ALIGNED BACKSIDE CONTACT IN NANOSHEET WITHOUT BDI simplified abstract (International Business Machines Corporation)

- 17945498. VTFET CIRCUIT WITH OPTIMIZED OUTPUT simplified abstract (International Business Machines Corporation)

- 17946002. DIODES IN NANOSHEET TECHNOLOGY simplified abstract (International Business Machines Corporation)

- 17946017. COMPLEMENTARY METAL-OXIDE-SEMICONDUCTOR (CMOS) APPARATUS WITH SELF-ALIGNED BACKSIDE CONTACT simplified abstract (International Business Machines Corporation)

- 17946546. STACKED FETS WITH CONTACT PLACEHOLDER STRUCTURES simplified abstract (International Business Machines Corporation)

- 17946740. VIA RESISTANCE TO BACKSIDE POWER RAIL simplified abstract (International Business Machines Corporation)

- 17946821. SELF-ALIGNED BACKSIDE CONTACT simplified abstract (International Business Machines Corporation)

- 17948664. FLEXIBLE WIRING ARCHITECTURE FOR MULTI-DIE INTEGRATION simplified abstract (International Business Machines Corporation)

- 17948877. NANOSHEET STACKS WITH DIELECTRIC ISOLATION LAYERS simplified abstract (International Business Machines Corporation)

- 17949579. SRAM with Improved Program and Sensing Margin for Scaled Nanosheet Devices simplified abstract (International Business Machines Corporation)

- 17955974. Self-Aligned Wafer Backside Gate Signal with Airgap simplified abstract (International Business Machines Corporation)

- 17956114. SEMICONDUCTOR STRUCTURES WITH STACKED INTERCONNECTS simplified abstract (International Business Machines Corporation)

- 17956244. BACKSIDE MRAM WITH FRONTSIDE DEVICES simplified abstract (International Business Machines Corporation)

- 17956309. EXTENDED EPITAXIAL GROWTH FOR IMPROVED CONTACT RESISTANCE simplified abstract (International Business Machines Corporation)

- 17956918. BACKSIDE CONTACT WITH SHALLOW PLACEHOLDER AND EASY BACKSIDE SEMICONDUCTOR REMOVAL simplified abstract (International Business Machines Corporation)

- 17957194. HYBRID INSERTED DIELECRIC GATE-ALL-AROUND DEVICE simplified abstract (International Business Machines Corporation)

- 17957599. VTFETS WITH WRAP-AROUND BACKSIDE CONTACTS simplified abstract (International Business Machines Corporation)

- 17960116. INNER SPACER RELIABILITY MACRO DESIGN AND WELL CONTACT FORMATION simplified abstract (International Business Machines Corporation)

- 17960222. STACKED-FET SRAM CELL WITH BOTTOM pFET simplified abstract (International Business Machines Corporation)

- 17961281. Backside BPR/BSPDN Intergration with Backside Local Interconnect. simplified abstract (International Business Machines Corporation)

- 17961774. HIGH DENSITY TRENCH CAPACITOR simplified abstract (International Business Machines Corporation)

- 17963031. SEMICONDUCTOR STRUCTURE WITH CONDUCTIVE SPACER IN SHALLOW TRENCH ISOLATION REGION simplified abstract (International Business Machines Corporation)

- 17963281. SKIP VIA WITH LATERAL LINE CONNECTION simplified abstract (International Business Machines Corporation)

- 17969260. Local VDD And VSS Power Supply Through Dummy Gates with Gate Tie-Downs and Associated Benefits simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17972892. Hybrid Power Rail Formation in Dielectric Isolation for Semiconductor Device simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 17986276. BACKSIDE SKIP-LEVEL THROUGH VIA FOR BACKSIDE SIGNAL LINE CONNECTION simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 18045181. FORMING SOURCE/DRAIN REGION IN STACKED FET STRUCTURE simplified abstract (International Business Machines Corporation)

- 18048877. ISOLATION RAIL BETWEEN BACKSIDE POWER RAILS simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 18049297. SOURCE/DRAIN CONTACT AT TIGHT CELL BOUNDARY simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 18049301. VIRTUAL POWER SUPPLY THROUGH WAFER BACKSIDE simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 18054160. BACKSIDE PROGRAMMABLE GATE ARRAY simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 18054161. BACKSIDE PROGRAMMABLE MEMORY simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 18054187. METHOD AND STRUCTURE OF FORMING BARRIER-LESS SKIP VIA WITH SUBTRACTIVE METAL PATTERNING simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 18054194. STACKED FET WITH EXTREMELY SMALL CELL HEIGHT simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 18054958. SPACER CUT FOR ASYMMETRIC SOURCE/DRAIN EPITAXIAL STRUCTURE IN STACKED FET simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 18054991. AIRGAP SPACER FOR POWER VIA simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 18059093. SUPPORT DIELECTRIC FIN TO PREVENT GATE FLOP-OVER IN NANOSHEET TRANSISTORS simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 18059098. ADJACENT BURIED POWER RAIL FOR STACKED FIELD-EFFECT TRANSISTOR ARCHITECTURE simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 18059672. THREE DIMENSIONAL RERAM DEVICE simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 18060003. LOCAL INTERCONNECT FORMATION AT DOUBLE DIFFUSION BREAK simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 18060056. LATE MIDDLE-OF-LINE GATE CUT WITH POWER BAR FORMATION simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 18060168. ISOLATED SUPER VIA TO MIDDLE METAL LINE LEVEL simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 18060544. BURIED OXIDE LAYER AND ETCH STOP LAYER PROCESS FOR DIRECT BACK SIDE CONTACT OF SEMICONDUCTOR DEVICE simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 18062624. POWER TAP CELL FOR FRONT SIDE POWER RAIL CONNECTION TO BSPDN simplified abstract (International Business Machines Corporation)

- 18063956. STACKED AND NON-STACKED TRANSISTORS WITH DOUBLE-SIDED INTERCONNECTS simplified abstract (International Business Machines Corporation)

- 18063987. VERTICAL TRANSPORT FIELD-EFFECT TRANSISTOR WITH LATE FIN CUT simplified abstract (International Business Machines Corporation)

- 18064260. PREVENTING SOURCE/DRAIN EPI MERGE WITHOUT CELL SIZE INCREASE simplified abstract (International Business Machines Corporation)

- 18064954. ENLARGED OVERLAP BETWEEN BACKSIDE POWER RAIL AND BACKSIDE CONTACT simplified abstract (International Business Machines Corporation)

- 18065060. BACKSIDE DIRECT CONTACT FORMATION simplified abstract (International Business Machines Corporation)

- 18065117. EMBEDDED ReRAM WITH BACKSIDE CONTACT simplified abstract (International Business Machines Corporation)

- 18065663. LOW RESISTANCE METALIZATION FOR CONNECTING A VERTICAL TRANSPORT FET SINGLE-CPP INVERTER simplified abstract (International Business Machines Corporation)

- 18065747. SKIP VIA WITH DISCONTINUOUS DIELECTRIC CAP simplified abstract (International Business Machines Corporation)

- 18065860. STACKED CMOS DEVICES WITH TWO DIELECTRIC MATERIALS IN A GATE CUT simplified abstract (International Business Machines Corporation)

- 18065923. TWO-TRANSISTOR CHIP AND THREE-TRANSISTOR CHIP IDENTIFICATION BIT CELLS simplified abstract (International Business Machines Corporation)

- 18065965. SELF-ALIGNED BACKSIDE GATE CONTACTS simplified abstract (International Business Machines Corporation)

- 18066243. CONTACT STRUCTURE FOR POWER DELIVERY ON SEMICONDUCTOR DEVICE simplified abstract (International Business Machines Corporation)

- 18066620. ENLARGED SHALLOW TRENCH ISOLATION FOR BACKSIDE POWER simplified abstract (International Business Machines Corporation)

- 18066671. STRUCTURE AND METHOD TO FORM VIA TO BACKSIDE POWER RAIL WITHOUT SHORTING TO GATE TIP simplified abstract (International Business Machines Corporation)

- 18067127. LOW-RESISTANCE VIA TO BACKSIDE POWER RAIL simplified abstract (International Business Machines Corporation)

- 18067148. HYBRID CELL HEIGHT DESIGN WITH A BACKSIDE POWER DISTRIBUTION NETWORK simplified abstract (International Business Machines Corporation)

- 18067207. HEAT DISSIPATION STRUCTURES FOR BONDED WAFERS simplified abstract (International Business Machines Corporation)

- 18067710. SELF-ALIGNED GATE METAL WITH TOP-DIELECTRIC ISOLATION simplified abstract (International Business Machines Corporation)

- 18067748. SEMICONDUCTOR DEVICE WITH BACKSIDE U-SHAPED SILICIDE simplified abstract (International Business Machines Corporation)

- 18068570. GATE TIE-DOWN FOR TOP FIELD EFFECT TRANSISTOR simplified abstract (International Business Machines Corporation)

- 18069077. VERTICAL FIELD EFFECT TRANSISTOR WITH SELF-ALIGNED BACKSIDE TRENCH EPITAXY simplified abstract (International Business Machines Corporation)

- 18069769. RESISTIVE RANDOM ACCESS MEMORY ON A BURIED BITLINE simplified abstract (International Business Machines Corporation)

- 18069970. EXTENDED SOURCE/DRAIN CONTACT FOR SHIFTED DRAIN VOLTAGE FOR A BACKSIDE POWER DISTRIBUTION NETWORK simplified abstract (International Business Machines Corporation)

- 18072675. PHASE CHANGE MEMORY simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 18078454. SEMICONDUCTOR STRUCTURE WITH BACKSIDE METALLIZATION LAYERS simplified abstract (International Business Machines Corporation)

- 18079079. CIRCUIT LAYOUTS WITH VARIABLE CIRCUIT CELL HEIGHTS IN THE SAME CIRCUIT ROW simplified abstract (International Business Machines Corporation)

- 18080029. BACKSIDE POWER DISTRIBUTION NETWORK SUBSTRATE USING A LATTICE MATCHED ETCH STOP LAYER simplified abstract (International Business Machines Corporation)

- 18080828. TRANSISTORS WITH DIELECTRIC STACK ISOLATING BACKSIDE POWER RAIL simplified abstract (International Business Machines Corporation)

- 18080892. DIFFUSION BREAK STRUCTURE FOR TRANSISTORS simplified abstract (International Business Machines Corporation)

- 18081795. STACKED VERTICAL-TRANSPORT FIELD EFFECT TRANSISTORS (VTFETs) simplified abstract (International Business Machines Corporation)

- 18083380. DIELECTRIC FILLED ALIGNMENT MARK STRUCTURES simplified abstract (International Business Machines Corporation)

- 18083818. FLEXIBLE MOL AND/OR BEOL STRUCTURE simplified abstract (International Business Machines Corporation)

- 18086229. VTFET CIRCUIT WITH OPTIMIZED MOL simplified abstract (International Business Machines Corporation)

- 18087990. GATE-ALL-AROUND TRANSISTORS WITH CLADDED SOURCE/DRAIN REGIONS simplified abstract (International Business Machines Corporation)

- 18089634. HYBRID CMOS WITH FIN AND NANOSHEET ARCHITECTURES simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 18089655. BACKSIDE CONTACTS FOR STACKED FIELD EFFECT TRANSISTORS simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 18089670. FERROELECTRIC-RAM WITH INTEGRATED DOMAIN REVERSAL CATALYST simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 18091997. BACK SIDE CONTACTS FOR SEMICONDUCTOR DEVICES simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 18092126. CELL-BASED SIGNAL CONNECTIVITY BETWEEN WAFER FRONTSIDE AND BACKSIDE simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 18093713. VIA STRUCTURE WITHOUT LINER INTERFACE simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 18093932. CMOS TOP SOURCE/DRAIN REGION DOPING AND EPITAXIAL GROWTH FOR A VERTICAL FIELD EFFECT TRANSISTOR simplified abstract (International Business Machines Corporation)

- 18097185. HYBRID SIGNAL ROUTING WITH BACKSIDE INTERCONNECT simplified abstract (International Business Machines Corporation)

- 18112020. MEMORY STRUCTURES HAVING A SINGLE ACCESS TRANSISTOR FOR MULTIPLE MEMORY DEVICES simplified abstract (International Business Machines Corporation)

- 18123613. BACKSIDE POWER ISLANDS FOR BACKSIDE POWER APPLICATIONS simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 18145003. FORK SHEET DEVICE WITH WRAPPED SOURCE AND DRAIN CONTACT TO PREVENT NFET TO PFET CONTACT SHORTAGE IN A TIGHT SPACE simplified abstract (International Business Machines Corporation)

- 18145034. STACKED TRANSISTORS HAVING SELF ALIGNED BACKSIDE CONTACT WITH BACKSIDE REPLACEMENT METAL GATE simplified abstract (International Business Machines Corporation)

- 18145059. VTFET CELL BOUNDARY HAVING AN IN-LINE CONTACT simplified abstract (International Business Machines Corporation)

- 18145840. DECOUPLING MIM CAPACITOR simplified abstract (International Business Machines Corporation)

- 18146988. FORMATION OF NON-SELF-ALIGNED BACKSIDE CONTACT simplified abstract (International Business Machines Corporation)

- 18147129. SEAMED RESISTIVE RANDOM ACCESS MEMORY CELL simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 18147699. INVERTER WITH BACKSIDE POWER DELIVERY NETWORK simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 18148392. RELAXED PITCH BACKSIDE MAGNETO-RESISTIVE RANDOM ACCESS MEMORY INTEGRATION WITH SELF-ALIGNED MICRO STUD AND BACKSIDE POWER DISTRIBUTION NETWORK simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 18150814. SEMICONDUCTOR TRANSISTOR ARRAYS simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 18155784. HETEROGENEOUS INTEGRATION OF DEVICE DIE HAVING BSPDN simplified abstract (International Business Machines Corporation)

- 18156024. FORMING WRAP AROUND CONTACT WITH SELF-ALIGNED BACKSIDE CONTACT simplified abstract (International Business Machines Corporation)

- 18158505. BACKSIDE CONTACT WITH CONTACT JUMPER FOR STACKED FET simplified abstract (International Business Machines Corporation)

- 18171528. NONLINEAR CHANNEL simplified abstract (International Business Machines Corporation)

- 18176551. SELF-ALIGNED BACKSIDE INTERCONNECT STRUCTURES simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 18177171. BACKSIDE GATE VIA STRUCTURE USING SELF-ALIGNED SCHEME simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 18178570. FRONTSIDE TO BACKSIDE SIGNAL VIA IN EDGE CELL simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 18179511. STACKED UPPER TRANSISTOR AND LOWER TRANSISTOR simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 18182412. SELF-ALIGNED VIA IN DOUBLE DIFFUSION BREAK TO CONNECT TO BACKSIDE INTERCONNECTS simplified abstract (International Business Machines Corporation)

- 18183189. METHOD AND STRUCTURE OF ACCURATELY CONTROLLING CONTACT GOUGING POSITION simplified abstract (International Business Machines Corporation)

- 18186227. FLEXIBLE SELF-ALIGNED POWER VIA SHAPE WITH GATE CUT FIRST simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- 18186229. STACKED RESISTIVE RANDOM-ACCESS MEMORY CROSS-POINT CELL simplified abstract (INTERNATIONAL BUSINESS MACHINES CORPORATION)

- Tao Li of Slingerlands NY (US)

- Brent A. Anderson of Jericho VT (US)

- Julien Frougier of Albany NY (US)

- Lawrence A. Clevenger of Saratoga Springs NY (US)

- Albert M. Chu of Nashua NH (US)

- Nicholas Anthony Lanzillo of Wynantskill NY (US)

- Min Gyu Sung of Latham NY (US)

- Kisik Choi of Watervliet NY (US)

- Junli Wang of Slingerlands NY (US)

- Juntao Li of Cohoes NY (US)

- Tsung-Sheng Kang of Ballston Lake NY (US)

- Tenko Yamashita of Schenectady NY (US)

- Chanro Park of Clifton Park NY (US)

- Shay Reboh of Guilderland NY (US)

- Shahrukh Khan of Sandy Hook CT (US)

- LEI ZHUANG of Ridgefield CT (US)

- Nicolas Jean Loubet of GUILDERLAND NY (US)

- Koichi Motoyama of Clifton Park NY (US)

- Jay William Strane of Wappingers Falls NY (US)

- James P. Mazza of Saratoga Springs NY (US)

- Nicholas Alexander POLOMOFF of Hopewell Junction NY (US)

- Matthew Stephen Angyal of Stormville NY (US)

- Terence Hook of Jericho Center VT (US)

- Reinaldo Vega of Mahopac NY (US)

- HUIMEI ZHOU of Albany NY (US)

- FEE LI LIE of Albany NY (US)

- John Christopher Arnold of North Chatham NY (US)

- Chen Zhang of Santa Clara CA (US)

- Lijuan Zou of Slingerlands NY (US)

- Jingyun Zhang of Albany NY (US)

- Biswanath Senapati of Mechanicville NY (US)

- JENS HAETTY of Halfmoon NY (US)

- Christopher Murphy of Red Hook NY (US)

- Chih-Chao Yang of Glenmont NY (US)

- Iqbal Rashid Saraf of Glenmont NY (US)

- Liqiao Qin of Albany NY (US)

- Nicholas Alexander Polomoff of Hopewell Junction NY (US)

- Huimei Zhou of Albany NY (US)

- Terence B. Hook of Jericho Center VT (US)

- Dan Moy of Bethel CT (US)

- Nicolas Jean Loubet of Guilderland NY (US)

- Sagarika Mukesh of Albany NY (US)

- Alexander Reznicek of Troy NY (US)

- Leon Sigal of Monsey NY (US)

- Biswanath Senapati of Albany NY (US)

- FEE LI LIE of ALBANY NY (US)

- Jay William Strane of Wappinger Falls NY (US)

- Indira Seshadri of Niskayuna NY (US)

- FENG LIU of Niskayuna NY (US)

- Dureseti Chidambarrao of Weston CT (US)

- Ravikumar Ramachandran of Pleasantville NY (US)

- Anthony I. Chou of Guilderland NY (US)

- Albert M Chu of Nashua NH (US)

- Xiaoming Yang of Clifton Park NY (US)

- Huai Huang of Clifton Park NY (US)

- Hosadurga Shobha of Niskayuna NY (US)

- Atharv Jog of Albany NY (US)

- Susan Ng Emans of Albany NY (US)

- Miaomiao Wang of Albany NY (US)

- Baozhen Li of South Burlington VT (US)

- Yoo-Mi Lee of Montvale NJ (US)

- Utkarsh Bajpai of Delmar NY (US)

- Joshua M. Rubin of Albany NY (US)

- Shay Reboh of Albany NY (US)

- Takashi Ando of Eastchester NY (US)

- David Wolpert of Poughkeepsie NY (US)

- Julien Frougier of Frougier NY (US)

- Shogo Mochizuki of Mechanicville NY (US)

- Ruilong Xie of Niskayuna NY (US)

- Inventors

- Inventors filing patents with International Business Machines Corporation

- Inventors filing patents with INTERNATIONAL BUSINESS MACHINES CORPORATION