Category:Hung-Jui Kuo: Difference between revisions

Appearance

Updating Category:Hung-Jui_Kuo |

Wikipatents (talk | contribs) Updating Category:Hung-Jui_Kuo |

||

| (One intermediate revision by the same user not shown) | |||

| Line 2: | Line 2: | ||

=== Executive Summary === | === Executive Summary === | ||

Hung-Jui Kuo is an inventor who has filed | Hung-Jui Kuo is an inventor who has filed 12 patents. Their primary areas of innovation include {Multilayer substrates ( (6 patents), SEMICONDUCTOR DEVICES NOT COVERED BY CLASS (5 patents), SEMICONDUCTOR DEVICES NOT COVERED BY CLASS (5 patents), and they have worked with companies such as Taiwan Semiconductor Manufacturing Company, Ltd. (10 patents), Taiwan Semiconductor Manufacturing Company Limited (2 patents). Their most frequent collaborators include [[Category:Yu-Hsiang Hu|Yu-Hsiang Hu]] (6 collaborations), [[Category:Jhih-Yu Wang|Jhih-Yu Wang]] (4 collaborations), [[Category:Po-Han Wang|Po-Han Wang]] (3 collaborations). | ||

=== Patent Filing Activity === | === Patent Filing Activity === | ||

| Line 11: | Line 11: | ||

==== List of Technology Areas ==== | ==== List of Technology Areas ==== | ||

* [[:Category:CPC_H01L23/3128|H01L23/3128]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): | * [[:Category:CPC_H01L23/5383|H01L23/5383]] ({Multilayer substrates (): 6 patents | ||

* [[:Category:CPC_H01L21/4853|H01L21/4853]] (Manufacture or treatment of parts, e.g. containers, prior to assembly of the devices, using processes not provided for in a single one of the subgroups): | * [[:Category:CPC_H01L21/568|H01L21/568]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 5 patents | ||

* [[:Category:CPC_H01L21/4857|H01L21/4857]] (Manufacture or treatment of parts, e.g. containers, prior to assembly of the devices, using processes not provided for in a single one of the subgroups): | * [[:Category:CPC_H01L23/3128|H01L23/3128]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 5 patents | ||

* [[:Category:CPC_H01L21/565|H01L21/565]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): | * [[:Category:CPC_H01L23/5389|H01L23/5389]] (the interconnection structure between a plurality of semiconductor chips being formed on, or in, insulating substrates ({): 4 patents | ||

* [[:Category:CPC_H01L21/4853|H01L21/4853]] (Manufacture or treatment of parts, e.g. containers, prior to assembly of the devices, using processes not provided for in a single one of the subgroups): 4 patents | |||

* [[:Category:CPC_H01L23/5386|H01L23/5386]] (the interconnection structure between a plurality of semiconductor chips being formed on, or in, insulating substrates ({): | * [[:Category:CPC_H01L21/4857|H01L21/4857]] (Manufacture or treatment of parts, e.g. containers, prior to assembly of the devices, using processes not provided for in a single one of the subgroups): 4 patents | ||

* [[:Category:CPC_H01L23/ | * [[:Category:CPC_H01L21/565|H01L21/565]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 4 patents | ||

* [[:Category: | * [[:Category:CPC_H01L23/5386|H01L23/5386]] (the interconnection structure between a plurality of semiconductor chips being formed on, or in, insulating substrates ({): 4 patents | ||

* [[:Category: | * [[:Category:CPC_H01L24/19|H01L24/19]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 4 patents | ||

* [[:Category: | * [[:Category:CPC_H01L24/20|H01L24/20]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 4 patents | ||

* [[:Category:CPC_H01L21/ | * [[:Category:CPC_H01L2224/214|H01L2224/214]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 4 patents | ||

* [[:Category:CPC_H01L23/544|H01L23/544]] (Marks applied to semiconductor devices {or parts}, e.g. registration marks, {alignment structures, wafer maps (test patterns for characterising or monitoring manufacturing processes): 3 patents | |||

* [[:Category:CPC_H01L2223/54426|H01L2223/54426]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 3 patents | |||

* [[:Category:CPC_H01L25/105|H01L25/105]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 3 patents | |||

* [[:Category:CPC_H01L21/4864|H01L21/4864]] (Manufacture or treatment of parts, e.g. containers, prior to assembly of the devices, using processes not provided for in a single one of the subgroups): 2 patents | |||

* [[:Category:CPC_H01L21/6835|H01L21/6835]] ({using temporarily an auxiliary support}): 2 patents | |||

* [[:Category:CPC_H01L23/564|H01L23/564]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents | |||

* [[:Category:CPC_H01L2221/68372|H01L2221/68372]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents | |||

* [[:Category:CPC_H01L21/78|H01L21/78]] (with subsequent division of the substrate into plural individual devices (cutting to change the surface-physical characteristics or shape of semiconductor bodies): 2 patents | |||

* [[:Category:CPC_H01L23/5384|H01L23/5384]] ({Conductive vias through the substrate with or without pins, e.g. buried coaxial conductors (): 2 patents | |||

* [[:Category:CPC_H01L24/32|H01L24/32]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents | |||

* [[:Category:CPC_H01L21/56|H01L21/56]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents | * [[:Category:CPC_H01L21/56|H01L21/56]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents | ||

* [[:Category:CPC_H01L23/31|H01L23/31]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents | * [[:Category:CPC_H01L23/31|H01L23/31]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents | ||

* [[:Category:CPC_H01L23/528|H01L23/528]] ({Geometry or} layout of the interconnection structure {(): 2 patents | * [[:Category:CPC_H01L23/528|H01L23/528]] ({Geometry or} layout of the interconnection structure {(): 2 patents | ||

* [[:Category:CPC_H01L23/481|H01L23/481]] (Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements {; Selection of materials therefor}): 2 patents | |||

* [[:Category:CPC_H01L23/49822|H01L23/49822]] ({Multilayer substrates (multilayer metallisation on monolayer substrate): 2 patents | * [[:Category:CPC_H01L23/49822|H01L23/49822]] ({Multilayer substrates (multilayer metallisation on monolayer substrate): 2 patents | ||

* [[:Category:CPC_H01L23/ | * [[:Category:CPC_H01L23/3121|H01L23/3121]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

* [[:Category:CPC_H01L23/562|H01L23/562]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | |||

* [[:Category:CPC_H01L23/585|H01L23/585]] ({comprising conductive layers or plates or strips or rods or rings (): 1 patents | |||

* [[:Category:CPC_H01L21/68742|H01L21/68742]] (using mechanical means, e.g. chucks, clamps or pinches {(using elecrostatic chucks): 1 patents | |||

* [[:Category:CPC_G03F7/70708|G03F7/70708]] (PHOTOMECHANICAL PRODUCTION OF TEXTURED OR PATTERNED SURFACES, e.g. FOR PRINTING, FOR PROCESSING OF SEMICONDUCTOR DEVICES; MATERIALS THEREFOR; ORIGINALS THEREFOR; APPARATUS SPECIALLY ADAPTED THEREFOR; (phototypographic composing devices): 1 patents | |||

* [[:Category:CPC_H01L21/561|H01L21/561]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | |||

* [[:Category:CPC_H01L23/5385|H01L23/5385]] (the interconnection structure between a plurality of semiconductor chips being formed on, or in, insulating substrates ({): 1 patents | |||

* [[:Category:CPC_H01L24/16|H01L24/16]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | |||

* [[:Category:CPC_H01L24/73|H01L24/73]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | |||

* [[:Category:CPC_H01L2224/16235|H01L2224/16235]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | |||

* [[:Category:CPC_H01L2224/32225|H01L2224/32225]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | |||

* [[:Category:CPC_H01L2224/73204|H01L2224/73204]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | |||

* [[:Category:CPC_H01L2924/364|H01L2924/364]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | * [[:Category:CPC_H01L2924/364|H01L2924/364]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

* [[:Category:CPC_G03F7/426|G03F7/426]] ({containing organic halogen compounds; containing organic sulfonic acids or salts thereof; containing sulfoxides}): 1 patents | * [[:Category:CPC_G03F7/426|G03F7/426]] ({containing organic halogen compounds; containing organic sulfonic acids or salts thereof; containing sulfoxides}): 1 patents | ||

* [[:Category:CPC_H01L23/5226|H01L23/5226]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | * [[:Category:CPC_H01L23/5226|H01L23/5226]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

* [[:Category:CPC_H01L21/76802|H01L21/76802]] (Applying interconnections to be used for carrying current between separate components within a device {comprising conductors and dielectrics}): 1 patents | * [[:Category:CPC_H01L21/76802|H01L21/76802]] (Applying interconnections to be used for carrying current between separate components within a device {comprising conductors and dielectrics}): 1 patents | ||

* [[:Category: | * [[:Category:CPC_H01L24/03|H01L24/03]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

* [[:Category:CPC_H01L24/05|H01L24/05]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | |||

* [[:Category:CPC_H01L2224/0346|H01L2224/0346]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | |||

* [[:Category:CPC_H01L2224/05546|H01L2224/05546]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | |||

* [[:Category:CPC_H01L21/76898|H01L21/76898]] ({formed through a semiconductor substrate}): 1 patents | * [[:Category:CPC_H01L21/76898|H01L21/76898]] ({formed through a semiconductor substrate}): 1 patents | ||

* [[:Category:CPC_H01L21/76804|H01L21/76804]] ({by forming tapered via holes}): 1 patents | * [[:Category:CPC_H01L21/76804|H01L21/76804]] ({by forming tapered via holes}): 1 patents | ||

* [[:Category:CPC_H01L21/76846|H01L21/76846]] ({Layer combinations}): 1 patents | * [[:Category:CPC_H01L21/76846|H01L21/76846]] ({Layer combinations}): 1 patents | ||

* [[:Category:CPC_H01L21/76871|H01L21/76871]] ({Layers specifically deposited to enhance or enable the nucleation of further layers, i.e. seed layers}): 1 patents | * [[:Category:CPC_H01L21/76871|H01L21/76871]] ({Layers specifically deposited to enhance or enable the nucleation of further layers, i.e. seed layers}): 1 patents | ||

* [[:Category:CPC_H01L23/49816|H01L23/49816]] (Leads, {i.e. metallisations or lead-frames} on insulating substrates, {e.g. chip carriers (shape of the substrate): 1 patents | * [[:Category:CPC_H01L23/49816|H01L23/49816]] (Leads, {i.e. metallisations or lead-frames} on insulating substrates, {e.g. chip carriers (shape of the substrate): 1 patents | ||

* [[:Category:CPC_H01L23/49838|H01L23/49838]] (Leads, {i.e. metallisations or lead-frames} on insulating substrates, {e.g. chip carriers (shape of the substrate): 1 patents | * [[:Category:CPC_H01L23/49838|H01L23/49838]] (Leads, {i.e. metallisations or lead-frames} on insulating substrates, {e.g. chip carriers (shape of the substrate): 1 patents | ||

| Line 47: | Line 67: | ||

* [[:Category:CPC_H01L25/50|H01L25/50]] ({Multistep manufacturing processes of assemblies consisting of devices, each device being of a type provided for in group): 1 patents | * [[:Category:CPC_H01L25/50|H01L25/50]] ({Multistep manufacturing processes of assemblies consisting of devices, each device being of a type provided for in group): 1 patents | ||

* [[:Category:CPC_H01L24/82|H01L24/82]] ({by forming build-up interconnects at chip-level, e.g. for high density interconnects [HDI] (interconnection structure between a plurality of semiconductor chips): 1 patents | * [[:Category:CPC_H01L24/82|H01L24/82]] ({by forming build-up interconnects at chip-level, e.g. for high density interconnects [HDI] (interconnection structure between a plurality of semiconductor chips): 1 patents | ||

* [[:Category:CPC_H01L24/80|H01L24/80]] ({Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected}): 1 patents | * [[:Category:CPC_H01L24/80|H01L24/80]] ({Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected}): 1 patents | ||

* [[:Category:CPC_H01L24/95|H01L24/95]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | * [[:Category:CPC_H01L24/95|H01L24/95]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| Line 54: | Line 73: | ||

* [[:Category:CPC_H01L2224/80896|H01L2224/80896]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | * [[:Category:CPC_H01L2224/80896|H01L2224/80896]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

* [[:Category:CPC_H01L24/13|H01L24/13]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | * [[:Category:CPC_H01L24/13|H01L24/13]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

* [[:Category:CPC_H01L25/0655|H01L25/0655]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | * [[:Category:CPC_H01L25/0655|H01L25/0655]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

* [[:Category:CPC_H01L2224/13007|H01L2224/13007]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | * [[:Category:CPC_H01L2224/13007|H01L2224/13007]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| Line 66: | Line 84: | ||

==== List of Companies ==== | ==== List of Companies ==== | ||

* Taiwan Semiconductor Manufacturing Company, Ltd.: | * Taiwan Semiconductor Manufacturing Company, Ltd.: 10 patents | ||

* Taiwan Semiconductor Manufacturing Company Limited: 2 patents | |||

=== Collaborators === | === Collaborators === | ||

* [[:Category:Yu-Hsiang Hu|Yu-Hsiang Hu]][[Category:Yu-Hsiang Hu]] (6 collaborations) | |||

* [[:Category:Jhih-Yu Wang|Jhih-Yu Wang]][[Category:Jhih-Yu Wang]] (4 collaborations) | |||

* [[:Category:Po-Han Wang|Po-Han Wang]][[Category:Po-Han Wang]] (3 collaborations) | |||

* [[:Category:Hui-Jung Tsai|Hui-Jung Tsai]][[Category:Hui-Jung Tsai]] (3 collaborations) | * [[:Category:Hui-Jung Tsai|Hui-Jung Tsai]][[Category:Hui-Jung Tsai]] (3 collaborations) | ||

* [[:Category:Yung-Chi Chu|Yung-Chi Chu]][[Category:Yung-Chi Chu]] (2 collaborations) | |||

* [[:Category:Sih-Hao Liao|Sih-Hao Liao]][[Category:Sih-Hao Liao]] (2 collaborations) | |||

* [[:Category:Ming-Che Ho|Ming-Che Ho]][[Category:Ming-Che Ho]] (2 collaborations) | * [[:Category:Ming-Che Ho|Ming-Che Ho]][[Category:Ming-Che Ho]] (2 collaborations) | ||

* [[:Category:Tai-Min Chang|Tai-Min Chang]][[Category:Tai-Min Chang]] (2 collaborations) | * [[:Category:Tai-Min Chang|Tai-Min Chang]][[Category:Tai-Min Chang]] (2 collaborations) | ||

* [[:Category:Meng-Che Tu|Meng-Che Tu]][[Category:Meng-Che Tu]] (2 collaborations) | * [[:Category:Meng-Che Tu|Meng-Che Tu]][[Category:Meng-Che Tu]] (2 collaborations) | ||

* [[:Category:Chia-Wei Wang|Chia-Wei Wang]][[Category:Chia-Wei Wang]] (2 collaborations) | * [[:Category:Chia-Wei Wang|Chia-Wei Wang]][[Category:Chia-Wei Wang]] (2 collaborations) | ||

* [[:Category:Wei-Yu Tsai|Wei-Yu Tsai]][[Category:Wei-Yu Tsai]] (1 collaborations) | |||

* [[:Category:Ming-Tan Lee|Ming-Tan Lee]][[Category:Ming-Tan Lee]] (1 collaborations) | |||

* [[:Category:Ching-Wen Chen|Ching-Wen Chen]][[Category:Ching-Wen Chen]] (1 collaborations) | * [[:Category:Ching-Wen Chen|Ching-Wen Chen]][[Category:Ching-Wen Chen]] (1 collaborations) | ||

* [[:Category:Wei-Chung Chang|Wei-Chung Chang]][[Category:Wei-Chung Chang]] (1 collaborations) | * [[:Category:Wei-Chung Chang|Wei-Chung Chang]][[Category:Wei-Chung Chang]] (1 collaborations) | ||

* [[:Category:Yu-Tzu Chang|Yu-Tzu Chang]][[Category:Yu-Tzu Chang]] (1 collaborations) | * [[:Category:Yu-Tzu Chang|Yu-Tzu Chang]][[Category:Yu-Tzu Chang]] (1 collaborations) | ||

[[Category:Hung-Jui Kuo]] | [[Category:Hung-Jui Kuo]] | ||

[[Category:Inventors]] | [[Category:Inventors]] | ||

[[Category:Inventors filing patents with Taiwan Semiconductor Manufacturing Company, Ltd.]] | [[Category:Inventors filing patents with Taiwan Semiconductor Manufacturing Company, Ltd.]] | ||

[[Category:Inventors filing patents with Taiwan Semiconductor Manufacturing Company Limited]] | |||

Latest revision as of 08:39, 2 May 2025

Hung-Jui Kuo

Executive Summary

Hung-Jui Kuo is an inventor who has filed 12 patents. Their primary areas of innovation include {Multilayer substrates ( (6 patents), SEMICONDUCTOR DEVICES NOT COVERED BY CLASS (5 patents), SEMICONDUCTOR DEVICES NOT COVERED BY CLASS (5 patents), and they have worked with companies such as Taiwan Semiconductor Manufacturing Company, Ltd. (10 patents), Taiwan Semiconductor Manufacturing Company Limited (2 patents). Their most frequent collaborators include (6 collaborations), (4 collaborations), (3 collaborations).

Patent Filing Activity

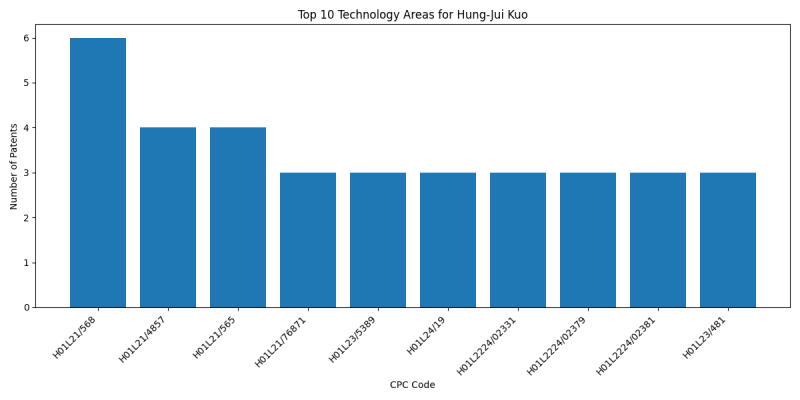

Technology Areas

List of Technology Areas

- H01L23/5383 ({Multilayer substrates (): 6 patents

- H01L21/568 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 5 patents

- H01L23/3128 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 5 patents

- H01L23/5389 (the interconnection structure between a plurality of semiconductor chips being formed on, or in, insulating substrates ({): 4 patents

- H01L21/4853 (Manufacture or treatment of parts, e.g. containers, prior to assembly of the devices, using processes not provided for in a single one of the subgroups): 4 patents

- H01L21/4857 (Manufacture or treatment of parts, e.g. containers, prior to assembly of the devices, using processes not provided for in a single one of the subgroups): 4 patents

- H01L21/565 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 4 patents

- H01L23/5386 (the interconnection structure between a plurality of semiconductor chips being formed on, or in, insulating substrates ({): 4 patents

- H01L24/19 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 4 patents

- H01L24/20 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 4 patents

- H01L2224/214 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 4 patents

- H01L23/544 (Marks applied to semiconductor devices {or parts}, e.g. registration marks, {alignment structures, wafer maps (test patterns for characterising or monitoring manufacturing processes): 3 patents

- H01L2223/54426 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 3 patents

- H01L25/105 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 3 patents

- H01L21/4864 (Manufacture or treatment of parts, e.g. containers, prior to assembly of the devices, using processes not provided for in a single one of the subgroups): 2 patents

- H01L21/6835 ({using temporarily an auxiliary support}): 2 patents

- H01L23/564 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L2221/68372 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L21/78 (with subsequent division of the substrate into plural individual devices (cutting to change the surface-physical characteristics or shape of semiconductor bodies): 2 patents

- H01L23/5384 ({Conductive vias through the substrate with or without pins, e.g. buried coaxial conductors (): 2 patents

- H01L24/32 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L21/56 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L23/31 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L23/528 ({Geometry or} layout of the interconnection structure {(): 2 patents

- H01L23/481 (Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements {; Selection of materials therefor}): 2 patents

- H01L23/49822 ({Multilayer substrates (multilayer metallisation on monolayer substrate): 2 patents

- H01L23/3121 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L23/562 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L23/585 ({comprising conductive layers or plates or strips or rods or rings (): 1 patents

- H01L21/68742 (using mechanical means, e.g. chucks, clamps or pinches {(using elecrostatic chucks): 1 patents

- G03F7/70708 (PHOTOMECHANICAL PRODUCTION OF TEXTURED OR PATTERNED SURFACES, e.g. FOR PRINTING, FOR PROCESSING OF SEMICONDUCTOR DEVICES; MATERIALS THEREFOR; ORIGINALS THEREFOR; APPARATUS SPECIALLY ADAPTED THEREFOR; (phototypographic composing devices): 1 patents

- H01L21/561 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L23/5385 (the interconnection structure between a plurality of semiconductor chips being formed on, or in, insulating substrates ({): 1 patents

- H01L24/16 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L24/73 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2224/16235 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2224/32225 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2224/73204 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2924/364 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- G03F7/426 ({containing organic halogen compounds; containing organic sulfonic acids or salts thereof; containing sulfoxides}): 1 patents

- H01L23/5226 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L21/76802 (Applying interconnections to be used for carrying current between separate components within a device {comprising conductors and dielectrics}): 1 patents

- H01L24/03 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L24/05 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2224/0346 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2224/05546 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L21/76898 ({formed through a semiconductor substrate}): 1 patents

- H01L21/76804 ({by forming tapered via holes}): 1 patents

- H01L21/76846 ({Layer combinations}): 1 patents

- H01L21/76871 ({Layers specifically deposited to enhance or enable the nucleation of further layers, i.e. seed layers}): 1 patents

- H01L23/49816 (Leads, {i.e. metallisations or lead-frames} on insulating substrates, {e.g. chip carriers (shape of the substrate): 1 patents

- H01L23/49838 (Leads, {i.e. metallisations or lead-frames} on insulating substrates, {e.g. chip carriers (shape of the substrate): 1 patents

- H01L2225/1041 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L24/14 ({of a plurality of bump connectors}): 1 patents

- H01L25/50 ({Multistep manufacturing processes of assemblies consisting of devices, each device being of a type provided for in group): 1 patents

- H01L24/82 ({by forming build-up interconnects at chip-level, e.g. for high density interconnects [HDI] (interconnection structure between a plurality of semiconductor chips): 1 patents

- H01L24/80 ({Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected}): 1 patents

- H01L24/95 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L25/0657 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H10D88/00 (No explanation available): 1 patents

- H01L2224/80896 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L24/13 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L25/0655 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2224/13007 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2224/32146 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2224/32235 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2924/15311 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2924/182 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

Companies

List of Companies

- Taiwan Semiconductor Manufacturing Company, Ltd.: 10 patents

- Taiwan Semiconductor Manufacturing Company Limited: 2 patents

Collaborators

- Yu-Hsiang Hu (6 collaborations)

- Jhih-Yu Wang (4 collaborations)

- Po-Han Wang (3 collaborations)

- Hui-Jung Tsai (3 collaborations)

- Yung-Chi Chu (2 collaborations)

- Sih-Hao Liao (2 collaborations)

- Ming-Che Ho (2 collaborations)

- Tai-Min Chang (2 collaborations)

- Meng-Che Tu (2 collaborations)

- Chia-Wei Wang (2 collaborations)

- Wei-Yu Tsai (1 collaborations)

- Ming-Tan Lee (1 collaborations)

- Ching-Wen Chen (1 collaborations)

- Wei-Chung Chang (1 collaborations)

- Yu-Tzu Chang (1 collaborations)

Categories:

- Yu-Hsiang Hu

- Jhih-Yu Wang

- Po-Han Wang

- Hui-Jung Tsai

- Yung-Chi Chu

- Sih-Hao Liao

- Ming-Che Ho

- Tai-Min Chang

- Meng-Che Tu

- Chia-Wei Wang

- Wei-Yu Tsai

- Ming-Tan Lee

- Ching-Wen Chen

- Wei-Chung Chang

- Yu-Tzu Chang

- Hung-Jui Kuo

- Inventors

- Inventors filing patents with Taiwan Semiconductor Manufacturing Company, Ltd.

- Inventors filing patents with Taiwan Semiconductor Manufacturing Company Limited