Category:Murong Lang of San Jose CA (US)

Contents

Murong Lang of San Jose CA (US)

Executive Summary

Murong Lang of San Jose CA (US) is an inventor who has filed 22 patents. Their primary areas of innovation include {Non-volatile semiconductor memory device, e.g. flash memory, one time programmable memory [OTP]} (10 patents), {Replication mechanisms} (6 patents), Digital input from, or digital output to, record carriers {, e.g. RAID, emulated record carriers or networked record carriers} (5 patents), and they have worked with companies such as Micron Technology, Inc. (20 patents), MICRON TECHNOLOGY, INC. (2 patents). Their most frequent collaborators include (20 collaborations), (5 collaborations), (5 collaborations).

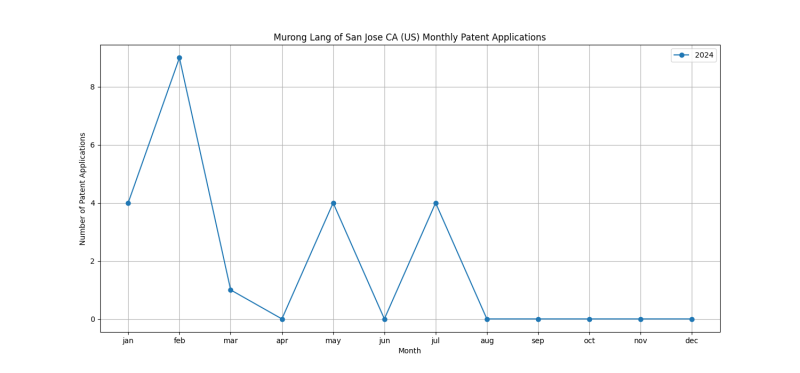

Patent Filing Activity

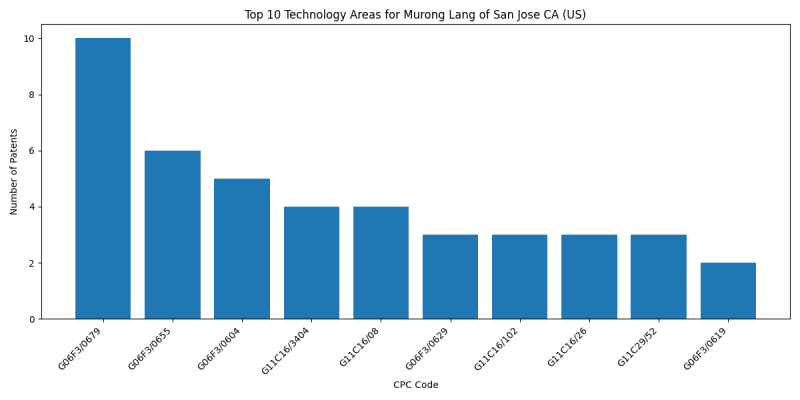

Technology Areas

List of Technology Areas

- G06F3/0679 ({Non-volatile semiconductor memory device, e.g. flash memory, one time programmable memory [OTP]}): 10 patents

- G06F3/0655 ({Replication mechanisms}): 6 patents

- G06F3/0604 (Digital input from, or digital output to, record carriers {, e.g. RAID, emulated record carriers or networked record carriers}): 5 patents

- G11C16/3404 ({Convergence or correction of memory cell threshold voltages; Repair or recovery of overerased or overprogrammed cells}): 4 patents

- G11C16/08 (Address circuits; Decoders; Word-line control circuits): 4 patents

- G06F3/0629 ({Configuration or reconfiguration of storage systems}): 3 patents

- G11C16/102 (Programming or data input circuits): 3 patents

- G11C16/26 (Sensing or reading circuits; Data output circuits): 3 patents

- G11C29/52 (STATIC STORES (semiconductor memory devices): 3 patents

- G06F3/0619 ({in relation to data integrity, e.g. data losses, bit errors}): 2 patents

- G06F3/0644 ({Management of space entities, e.g. partitions, extents, pools}): 2 patents

- G11C16/3495 ({Arrangements for evaluating degradation, retention or wearout, e.g. by counting erase cycles}): 2 patents

- G06F3/0611 ({in relation to response time}): 2 patents

- G06F3/0653 ({Monitoring storage devices or systems}): 2 patents

- G11C7/1063 (Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers): 1 patents

- G11C16/3481 (STATIC STORES (semiconductor memory devices): 1 patents

- G11C29/50004 (STATIC STORES (semiconductor memory devices): 1 patents

- G11C29/783 ({with refresh of replacement cells, e.g. in DRAMs}): 1 patents

- G11C16/28 (STATIC STORES (semiconductor memory devices): 1 patents

- G06F3/0652 ({Erasing, e.g. deleting, data cleaning, moving of data to a wastebasket}): 1 patents

- G11C16/16 (STATIC STORES (semiconductor memory devices): 1 patents

- G11C16/3445 ({Circuits or methods to verify correct erasure of nonvolatile memory cells}): 1 patents

- G06F3/061 (Digital input from, or digital output to, record carriers {, e.g. RAID, emulated record carriers or networked record carriers}): 1 patents

- G11C11/5628 ({Programming or writing circuits; Data input circuits}): 1 patents

- G11C11/5671 ({using charge trapping in an insulator}): 1 patents

- G11C16/0483 ({comprising cells having several storage transistors connected in series}): 1 patents

- G11C16/10 (Programming or data input circuits): 1 patents

- G06F3/064 ({Management of blocks}): 1 patents

- G11C16/3418 (STATIC STORES (semiconductor memory devices): 1 patents

- G11C16/349 ({Arrangements for evaluating degradation, retention or wearout, e.g. by counting erase cycles}): 1 patents

- G11C11/40618 (STATIC STORES (semiconductor memory devices): 1 patents

- G06F3/0616 ({in relation to life time, e.g. increasing Mean Time Between Failures [MTBF]}): 1 patents

- G06N20/00 (Machine learning): 1 patents

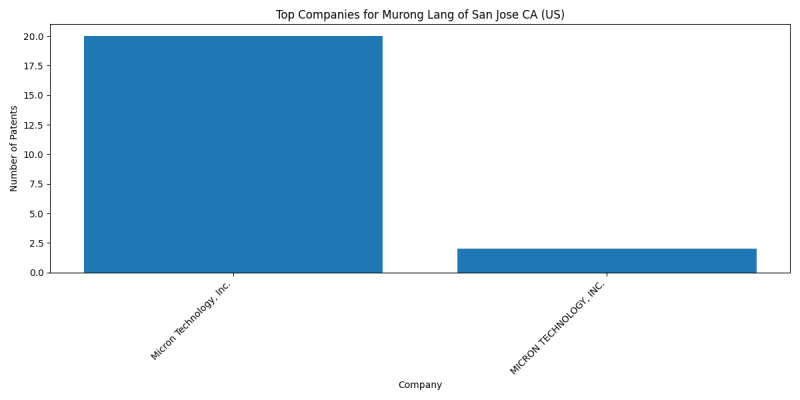

Companies

List of Companies

- Micron Technology, Inc.: 20 patents

- MICRON TECHNOLOGY, INC.: 2 patents

Collaborators

- Zhenming Zhou of San Jose CA (US) (20 collaborations)

- Zhongguang Xu of San Jose CA (US) (5 collaborations)

- Li-Te Chang of San Jose CA (US) (5 collaborations)

- Ching-Huang Lu of Fremont CA (US) (5 collaborations)

- Tingjun Xie of Milpitas CA (US) (3 collaborations)

- Jiangli Zhu of San Jose CA (US) (3 collaborations)

- Christina Papagianni of San Jose CA (US) (3 collaborations)

- Jian Huang of Union City CA (US) (3 collaborations)

- Yu-Chung Lien of San Jose CA (US) (3 collaborations)

- Peng Zhang of Los Altos CA (US) (2 collaborations)

- Charles See Yeung Kwong of Redwood City CA (US) (2 collaborations)

- Ting Luo of Santa Clara CA (US) (2 collaborations)

- Nagendra Prasad Ganesh Rao of Folsom CA (US) (2 collaborations)

- Fangfang Zhu of San Jose CA (US) (1 collaborations)

- Nicola Ciocchini of Boise ID (US) (1 collaborations)

- Zhenlei Shen of Milpitas CA (US) (1 collaborations)

- Ugo Russo of Boise ID (US) (1 collaborations)

- Niccolo' Righetti of Boise ID (US) (1 collaborations)

- Aaron Lee of Sunnyvale CA (US) (1 collaborations)

- Ronit Roneel Prakash (1 collaborations)

- Pitamber Shukla of Boise ID (US) (1 collaborations)

- Sead Zildzic of Folsom CA (US) (1 collaborations)

- Michael G. Miller of Boise ID (US) (1 collaborations)

- Li-Te Chang of Boise ID (US) (1 collaborations)

- Vamsi Pavan Rayaprolu of Santa Clara CA (US) (1 collaborations)

- Seungjune Jeon of Santa Clara CA (US) (1 collaborations)

Subcategories

This category has the following 3 subcategories, out of 3 total.

M

Y

Z

Pages in category "Murong Lang of San Jose CA (US)"

The following 42 pages are in this category, out of 42 total.

1

- 17823191. PARTIAL BLOCK READ VOLTAGE OFFSET simplified abstract (Micron Technology, Inc.)

- 17830625. ADAPTIVE ENHANCED CORRECTIVE READ BASED ON WRITE AND READ TEMPERATURE simplified abstract (Micron Technology, Inc.)

- 17842278. ERROR AVOIDANCE FOR PARTIALLY PROGRAMMED BLOCKS OF A MEMORY DEVICE simplified abstract (Micron Technology, Inc.)

- 17876346. MEMORY CELL VOLTAGE LEVEL SELECTION simplified abstract (Micron Technology, Inc.)

- 17888171. ADAPTIVE SENSING TIME FOR MEMORY OPERATIONS simplified abstract (Micron Technology, Inc.)

- 17894528. ADAPTIVE ERROR AVOIDANCE IN THE MEMORY DEVICES simplified abstract (Micron Technology, Inc.)

- 17897184. PADDING IN FLASH MEMORY BLOCKS simplified abstract (Micron Technology, Inc.)

- 17898043. NAND DETECT EMPTY PAGE SCAN simplified abstract (Micron Technology, Inc.)

- 17938153. APPARATUS WITH READ LEVEL MANAGEMENT AND METHODS FOR OPERATING THE SAME simplified abstract (Micron Technology, Inc.)

- 17938307. APPARATUS WITH READ LEVEL MANAGEMENT AND METHODS FOR OPERATING THE SAME simplified abstract (Micron Technology, Inc.)

- 18242884. PERFORMING SELECT GATE INTEGRITY CHECKS TO IDENTIFY AND INVALIDATE DEFECTIVE BLOCKS simplified abstract (MICRON TECHNOLOGY, INC.)

- 18421893. MODIFICATION OF PROGRAM VOLTAGE LEVEL WITH READ OR PROGRAM-VERIFY ADJUSTMENT FOR IMPROVING RELIABILITY IN MEMORY DEVICES simplified abstract (Micron Technology, Inc.)

- 18425383. SELECTIVE DATA PATTERN WRITE SCRUB FOR A MEMORY SYSTEM simplified abstract (Micron Technology, Inc.)

- 18434616. ADAPTIVE ENHANCED CORRECTIVE READ BASED ON WRITE AND READ TEMPERATURE simplified abstract (Micron Technology, Inc.)

- 18514926. OPTIMIZING DATA RELIABILITY USING ERASE RETENTION simplified abstract (Micron Technology, Inc.)

- 18519248. DYNAMIC READ CALIBRATION simplified abstract (Micron Technology, Inc.)

- 18610770. APPARATUS WITH TIME-BASED READ LEVEL MANAGEMENT AND METHODS FOR OPERATING THE SAME simplified abstract (Micron Technology, Inc.)

- 18617430. EMPTY PAGE SCAN OPERATIONS ADJUSTMENT simplified abstract (Micron Technology, Inc.)

- 18662940. ADAPTIVE TIME SENSE PARAMETERS AND OVERDRIVE VOLTAGE PARAMETERS FOR RESPECTIVE GROUPS OF WORDLINES IN A MEMORY SUB-SYSTEM simplified abstract (Micron Technology, Inc.)

- 18663978. ADAPTIVE SENSING TIME FOR MEMORY OPERATIONS simplified abstract (Micron Technology, Inc.)

- 18671855. ADAPTIVE TIME SENSE PARAMETERS AND OVERDRIVE VOLTAGE PARAMETERS FOR WORDLINES AT CORNER TEMPERATURES IN A MEMORY SUB-SYSTEM simplified abstract (Micron Technology, Inc.)

- 18672640. ERROR AVOIDANCE FOR PARTIALLY PROGRAMMED BLOCKS OF A MEMORY DEVICE simplified abstract (Micron Technology, Inc.)

- 18734724. REFRESH OF NEIGHBORING MEMORY CELLS BASED ON READ STATUS simplified abstract (Micron Technology, Inc.)

- 18739769. WORD LINE BASED PROGRAM VOLTAGE ADJUSTMENT (Micron Technology, Inc.)

M

- Micron technology, inc. (20240176496). OPTIMIZING DATA RELIABILITY USING ERASE RETENTION simplified abstract

- Micron technology, inc. (20240177795). DYNAMIC READ CALIBRATION simplified abstract

- Micron technology, inc. (20240231644). APPARATUS WITH TIME-BASED READ LEVEL MANAGEMENT AND METHODS FOR OPERATING THE SAME simplified abstract

- Micron technology, inc. (20240231666). EMPTY PAGE SCAN OPERATIONS ADJUSTMENT simplified abstract

- Micron technology, inc. (20240233843). SELECTIVE DATA PATTERN WRITE SCRUB FOR A MEMORY SYSTEM simplified abstract

- Micron technology, inc. (20240241664). ADAPTIVE ENHANCED CORRECTIVE READ BASED ON WRITE AND READ TEMPERATURE simplified abstract

- Micron technology, inc. (20240290404). GATE VOLTAGE STEP AND PROGRAM VERIFY LEVEL ADJUSTMENT IN A MEMORY DEVICE simplified abstract

- Micron technology, inc. (20240302967). ADAPTIVE SENSING TIME FOR MEMORY OPERATIONS simplified abstract

- Micron technology, inc. (20240311042). ADAPTIVE TIME SENSE PARAMETERS AND OVERDRIVE VOLTAGE PARAMETERS FOR WORDLINES AT CORNER TEMPERATURES IN A MEMORY SUB-SYSTEM simplified abstract

- Micron technology, inc. (20240311311). ERROR AVOIDANCE FOR PARTIALLY PROGRAMMED BLOCKS OF A MEMORY DEVICE simplified abstract

- Micron technology, inc. (20240312526). PARTIAL BLOCK HANDLING PROTOCOL IN A NON-VOLATILE MEMORY DEVICE simplified abstract

- Micron technology, inc. (20240319881). ADAPTIVE TIME SENSE PARAMETERS AND OVERDRIVE VOLTAGE PARAMETERS FOR RESPECTIVE GROUPS OF WORDLINES IN A MEMORY SUB-SYSTEM simplified abstract

- Micron technology, inc. (20240319886). MODIFICATION OF PROGRAM VOLTAGE LEVEL WITH READ OR PROGRAM-VERIFY ADJUSTMENT FOR IMPROVING RELIABILITY IN MEMORY DEVICES simplified abstract

- Micron technology, inc. (20240321350). REFRESH OF NEIGHBORING MEMORY CELLS BASED ON READ STATUS simplified abstract

- Micron technology, inc. (20240420784). WORD LINE BASED PROGRAM VOLTAGE ADJUSTMENT

U

- US Patent Application 17825439. PARTIAL BLOCK HANDLING PROTOCOL IN A NON-VOLATILE MEMORY DEVICE simplified abstract

- US Patent Application 17830625. ADAPTIVE ENHANCED CORRECTIVE READ BASED ON WRITE AND READ TEMPERATURE simplified abstract

- US Patent Application 17938307. APPARATUS WITH READ LEVEL MANAGEMENT AND METHODS FOR OPERATING THE SAME simplified abstract

- Zhenming Zhou of San Jose CA (US)

- Zhongguang Xu of San Jose CA (US)

- Li-Te Chang of San Jose CA (US)

- Ching-Huang Lu of Fremont CA (US)

- Tingjun Xie of Milpitas CA (US)

- Jiangli Zhu of San Jose CA (US)

- Christina Papagianni of San Jose CA (US)

- Jian Huang of Union City CA (US)

- Yu-Chung Lien of San Jose CA (US)

- Peng Zhang of Los Altos CA (US)

- Charles See Yeung Kwong of Redwood City CA (US)

- Ting Luo of Santa Clara CA (US)

- Nagendra Prasad Ganesh Rao of Folsom CA (US)

- Fangfang Zhu of San Jose CA (US)

- Nicola Ciocchini of Boise ID (US)

- Zhenlei Shen of Milpitas CA (US)

- Ugo Russo of Boise ID (US)

- Niccolo' Righetti of Boise ID (US)

- Aaron Lee of Sunnyvale CA (US)

- Ronit Roneel Prakash

- Pitamber Shukla of Boise ID (US)

- Sead Zildzic of Folsom CA (US)

- Michael G. Miller of Boise ID (US)

- Li-Te Chang of Boise ID (US)

- Vamsi Pavan Rayaprolu of Santa Clara CA (US)

- Seungjune Jeon of Santa Clara CA (US)

- Murong Lang of San Jose CA (US)

- Inventors

- Inventors filing patents with Micron Technology, Inc.

- Inventors filing patents with MICRON TECHNOLOGY, INC.