Category:Kang-Yong Kim of Boise ID (US)

Contents

Kang-Yong Kim of Boise ID (US)

Executive Summary

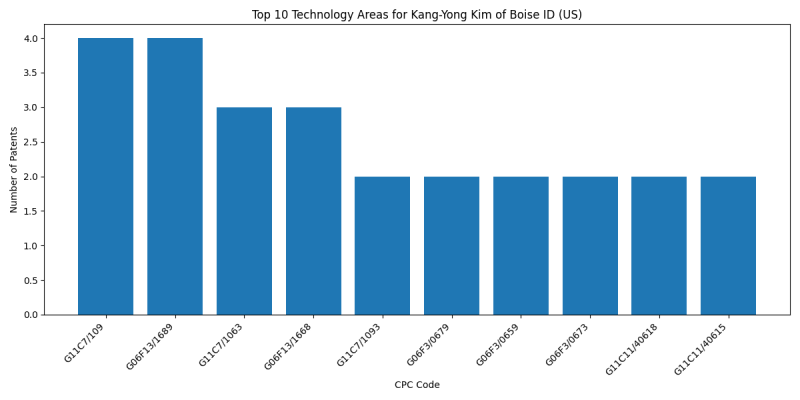

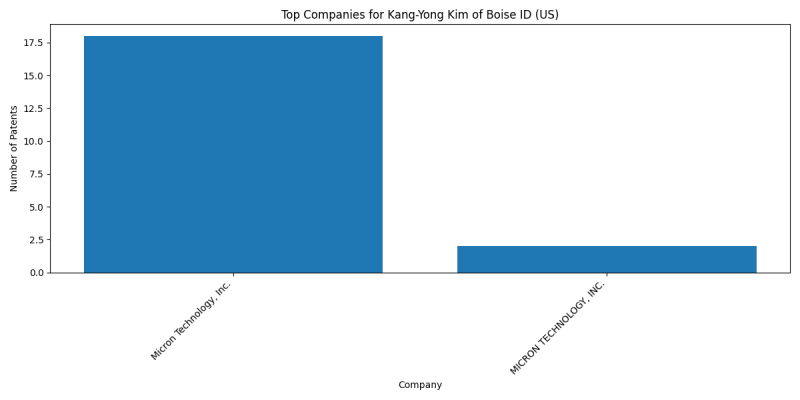

Kang-Yong Kim of Boise ID (US) is an inventor who has filed 20 patents. Their primary areas of innovation include Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers (4 patents), ELECTRIC DIGITAL DATA PROCESSING (computer systems based on specific computational models (4 patents), Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers (3 patents), and they have worked with companies such as Micron Technology, Inc. (18 patents), MICRON TECHNOLOGY, INC. (2 patents). Their most frequent collaborators include (11 collaborations), (7 collaborations), (3 collaborations).

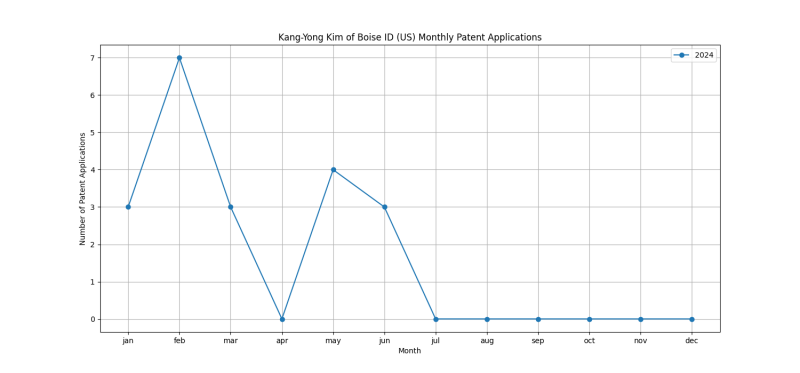

Patent Filing Activity

Technology Areas

List of Technology Areas

- G11C7/109 (Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers): 4 patents

- G06F13/1689 (ELECTRIC DIGITAL DATA PROCESSING (computer systems based on specific computational models): 4 patents

- G11C7/1063 (Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers): 3 patents

- G06F13/1668 (ELECTRIC DIGITAL DATA PROCESSING (computer systems based on specific computational models): 3 patents

- G11C7/1093 (Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers): 2 patents

- G06F3/0679 ({Non-volatile semiconductor memory device, e.g. flash memory, one time programmable memory [OTP]}): 2 patents

- G06F3/0659 ({Command handling arrangements, e.g. command buffers, queues, command scheduling}): 2 patents

- G06F3/0673 ({Single storage device}): 2 patents

- G11C11/40618 (STATIC STORES (semiconductor memory devices): 2 patents

- G11C11/40615 (STATIC STORES (semiconductor memory devices): 2 patents

- G06F13/4027 (ELECTRIC DIGITAL DATA PROCESSING (computer systems based on specific computational models): 2 patents

- G11C7/222 (Read-write [R-W] timing or clocking circuits; Read-write [R-W] control signal generators or management): 2 patents

- G11C11/4076 (Timing circuits (for regeneration management): 2 patents

- H03K5/1565 ({the output pulses having a constant duty cycle}): 2 patents

- G11C7/225 (Read-write [R-W] timing or clocking circuits; Read-write [R-W] control signal generators or management): 2 patents

- G11C7/1066 (Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers): 1 patents

- G11C7/1087 (Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers): 1 patents

- G11C7/22 (Read-write [R-W] timing or clocking circuits; Read-write [R-W] control signal generators or management): 1 patents

- G11C11/4093 (Input/output [I/O] data interface arrangements, e.g. data buffers): 1 patents

- G11C29/022 (STATIC STORES (semiconductor memory devices): 1 patents

- G11C29/028 (STATIC STORES (semiconductor memory devices): 1 patents

- G11C29/10 (STATIC STORES (semiconductor memory devices): 1 patents

- G06F3/0647 ({Migration mechanisms}): 1 patents

- G06F3/0616 ({in relation to life time, e.g. increasing Mean Time Between Failures [MTBF]}): 1 patents

- G06F3/0635 ({by changing the path, e.g. traffic rerouting, path reconfiguration}): 1 patents

- G06F3/0653 ({Monitoring storage devices or systems}): 1 patents

- G06F3/0683 ({Plurality of storage devices}): 1 patents

- G06F13/1684 (ELECTRIC DIGITAL DATA PROCESSING (computer systems based on specific computational models): 1 patents

- G06F13/4234 (Bus transfer protocol, e.g. handshake; Synchronisation): 1 patents

- G06F3/0614 ({Improving the reliability of storage systems}): 1 patents

- G06F12/0223 ({User address space allocation, e.g. contiguous or non contiguous base addressing}): 1 patents

- G06F12/023 ({Free address space management}): 1 patents

- G06F2212/1016 (ELECTRIC DIGITAL DATA PROCESSING (computer systems based on specific computational models): 1 patents

- G11C7/08 (Control thereof): 1 patents

- G11C7/1069 ({I/O lines read out arrangements}): 1 patents

- G11C29/52 (STATIC STORES (semiconductor memory devices): 1 patents

- G06F13/1621 (ELECTRIC DIGITAL DATA PROCESSING (computer systems based on specific computational models): 1 patents

- G06F13/4068 (ELECTRIC DIGITAL DATA PROCESSING (computer systems based on specific computational models): 1 patents

- G06F11/0772 (Responding to the occurrence of a fault, e.g. fault tolerance): 1 patents

- G06F13/1663 (ELECTRIC DIGITAL DATA PROCESSING (computer systems based on specific computational models): 1 patents

- G11C7/20 (STATIC STORES (semiconductor memory devices): 1 patents

- G11C11/40622 (STATIC STORES (semiconductor memory devices): 1 patents

- G11C11/4096 (Input/output [I/O] data management or control circuits, e.g. reading or writing circuits, I/O drivers or bit-line switches): 1 patents

- G11C11/408 (Address circuits): 1 patents

- G11C7/24 (STATIC STORES (semiconductor memory devices): 1 patents

- G11C29/18 (STATIC STORES (semiconductor memory devices): 1 patents

- G11C29/56004 (STATIC STORES (semiconductor memory devices): 1 patents

- G06F3/0619 ({in relation to data integrity, e.g. data losses, bit errors}): 1 patents

- G06F3/0656 ({Data buffering arrangements}): 1 patents

- G06F3/0629 ({Configuration or reconfiguration of storage systems}): 1 patents

- G06F3/061 (Digital input from, or digital output to, record carriers {, e.g. RAID, emulated record carriers or networked record carriers}): 1 patents

Companies

List of Companies

- Micron Technology, Inc.: 18 patents

- MICRON TECHNOLOGY, INC.: 2 patents

Collaborators

- Yang Lu of Boise ID (US) (11 collaborations)

- Hyun Yoo Lee of Boise ID (US) (7 collaborations)

- Smruti Subhash Jhaveri of Boise ID (US) (3 collaborations)

- John Christopher Sancon of Boise ID (US) (3 collaborations)

- Francesco Douglas Verna-Ketel of Boise ID (US) (2 collaborations)

- Hyunyoo Lee of Boise ID (US) (1 collaborations)

- Timothy M. Hollis of Meridian ID (US) (1 collaborations)

- Dong Soon Lim of Boise ID (US) (1 collaborations)

- Sourabh Dhir of Boise ID (US) (1 collaborations)

- Yang Lu (1 collaborations)

- Mark Kalei Hadrick of Boise ID (US) (1 collaborations)

- Yuan He of Boise ID (US) (1 collaborations)

- Jason McBride Brown of Austin TX (US) (1 collaborations)

- Venkatraghavan Bringivijayaraghavan (1 collaborations)

- Vijayakrishna J. Vankayala of Allen TX (US) (1 collaborations)

- Creston M. Dupree of Boise ID (US) (1 collaborations)

- Creston M. Dupree of San Jose CA (US) (1 collaborations)

- Erik T. Barmon of Boise ID (US) (1 collaborations)

- Nathaniel J. Meier of Boise ID (US) (1 collaborations)

- Yu-Sheng Hsu of San Jose CA (US) (1 collaborations)

- Ke Wei Chan (1 collaborations)

Subcategories

This category has only the following subcategory.

K

Pages in category "Kang-Yong Kim of Boise ID (US)"

The following 39 pages are in this category, out of 39 total.

1

- 17823407. Adaptive Memory Registers simplified abstract (Micron Technology, Inc.)

- 17823415. Bus Training with Interconnected Dice simplified abstract (Micron Technology, Inc.)

- 17823423. Bus Training with Interconnected Dice simplified abstract (Micron Technology, Inc.)

- 17823432. Erroneous Select Die Access (SDA) Detection simplified abstract (Micron Technology, Inc.)

- 17823443. Asymmetric Read-Write Sequence for Interconnected Dies simplified abstract (Micron Technology, Inc.)

- 17823450. Dynamic Address Scramble simplified abstract (Micron Technology, Inc.)

- 17823458. Die Disablement simplified abstract (Micron Technology, Inc.)

- 17944572. MEMORY CHANNEL DISABLEMENT simplified abstract (Micron Technology, Inc.)

- 17965957. MEMORY SYSTEM REFRESH MANAGEMENT simplified abstract (Micron Technology, Inc.)

- 18407062. INTERNAL AND EXTERNAL DATA TRANSFER FOR STACKED MEMORY DIES simplified abstract (Micron Technology, Inc.)

- 18420404. Programmable Memory Timing simplified abstract (Micron Technology, Inc.)

- 18520189. Sharable Usage-Based Disturbance Circuitry simplified abstract (Micron Technology, Inc.)

- 18582356. Automated Error Correction with Memory Refresh simplified abstract (Micron Technology, Inc.)

- 18604339. APPARATUSES AND METHODS INCLUDING MULTILEVEL COMMAND AND ADDRESS SIGNALS simplified abstract (Lodestar Licensing Group LLC)

- 18608591. MANAGING ADDRESS ACCESS INFORMATION simplified abstract (Micron Technology, Inc.)

- 18627859. Conflict Avoidance for Bank-Shared Circuitry that supports Usage-Based Disturbance Mitigation simplified abstract (Micron Technology, Inc.)

- 18627960. Data Sense Amplifier Circuit with a Hybrid Architecture simplified abstract (Micron Technology, Inc.)

- 18628127. Usage-Based Disturbance Counter Clearance simplified abstract (Micron Technology, Inc.)

- 18629445. APPARATUSES AND METHODS FOR TRACKING WORD LINE ACCESSES simplified abstract (Micron Technology, Inc.)

- 18647867. CENTRALIZED ERROR CORRECTION CIRCUIT simplified abstract (Micron Technology, Inc.)

- 18672339. DIE LOCATION DETECTION FOR GROUPED MEMORY DIES simplified abstract (Micron Technology, Inc.)

- 18680550. SELECTIVE ACCESS FOR GROUPED MEMORY DIES simplified abstract (Micron Technology, Inc.)

- 18734721. Equalization for Pulse-Amplitude Modulation simplified abstract (Micron Technology, Inc.)

M

- Micron technology, inc. (20240161794). INTERNAL AND EXTERNAL DATA TRANSFER FOR STACKED MEMORY DIES simplified abstract

- Micron technology, inc. (20240161796). Programmable Memory Timing simplified abstract

- Micron technology, inc. (20240177745). Sharable Usage-Based Disturbance Circuitry simplified abstract

- Micron technology, inc. (20240192862). Automated Error Correction with Memory Refresh simplified abstract

- Micron technology, inc. (20240201885). INTER-MEMORY MOVEMENT IN A MULTI-MEMORY SYSTEM simplified abstract

- Micron technology, inc. (20240202145). Memory Die Interconnections to Physical Layer Interfaces simplified abstract

- Micron technology, inc. (20240302998). MANAGING ADDRESS ACCESS INFORMATION simplified abstract

- Micron technology, inc. (20240312499). DIE LOCATION DETECTION FOR GROUPED MEMORY DIES simplified abstract

- Micron technology, inc. (20240321329). SELECTIVE ACCESS FOR GROUPED MEMORY DIES simplified abstract

- Micron technology, inc. (20240323062). Equalization for Pulse-Amplitude Modulation simplified abstract

- Micron technology, inc. (20240338126). Conflict Avoidance for Bank-Shared Circuitry that supports Usage-Based Disturbance Mitigation simplified abstract

- Micron technology, inc. (20240339152). Data Sense Amplifier Circuit with a Hybrid Architecture simplified abstract

- Micron technology, inc. (20240347096). Usage-Based Disturbance Counter Clearance simplified abstract

- Micron technology, inc. (20240347100). APPARATUSES AND METHODS FOR TRACKING WORD LINE ACCESSES simplified abstract

- Micron technology, inc. (20240347123). CENTRALIZED ERROR CORRECTION CIRCUIT simplified abstract

- Yang Lu of Boise ID (US)

- Hyun Yoo Lee of Boise ID (US)

- Smruti Subhash Jhaveri of Boise ID (US)

- John Christopher Sancon of Boise ID (US)

- Francesco Douglas Verna-Ketel of Boise ID (US)

- Hyunyoo Lee of Boise ID (US)

- Timothy M. Hollis of Meridian ID (US)

- Dong Soon Lim of Boise ID (US)

- Sourabh Dhir of Boise ID (US)

- Yang Lu

- Mark Kalei Hadrick of Boise ID (US)

- Yuan He of Boise ID (US)

- Jason McBride Brown of Austin TX (US)

- Venkatraghavan Bringivijayaraghavan

- Vijayakrishna J. Vankayala of Allen TX (US)

- Creston M. Dupree of Boise ID (US)

- Creston M. Dupree of San Jose CA (US)

- Erik T. Barmon of Boise ID (US)

- Nathaniel J. Meier of Boise ID (US)

- Yu-Sheng Hsu of San Jose CA (US)

- Ke Wei Chan

- Kang-Yong Kim of Boise ID (US)

- Inventors

- Inventors filing patents with Micron Technology, Inc.

- Inventors filing patents with MICRON TECHNOLOGY, INC.