Category:Chung-Te Lin

Jump to navigation

Jump to search

Contents

Chung-Te Lin

Executive Summary

Chung-Te Lin is an inventor who has filed 27 patents. Their primary areas of innovation include ELECTRONIC MEMORY DEVICES (8 patents), SEMICONDUCTOR DEVICES NOT COVERED BY CLASS (7 patents), SEMICONDUCTOR DEVICES NOT COVERED BY CLASS (7 patents), and they have worked with companies such as Taiwan Semiconductor Manufacturing Company, Ltd. (27 patents). Their most frequent collaborators include (11 collaborations), (8 collaborations), (6 collaborations).

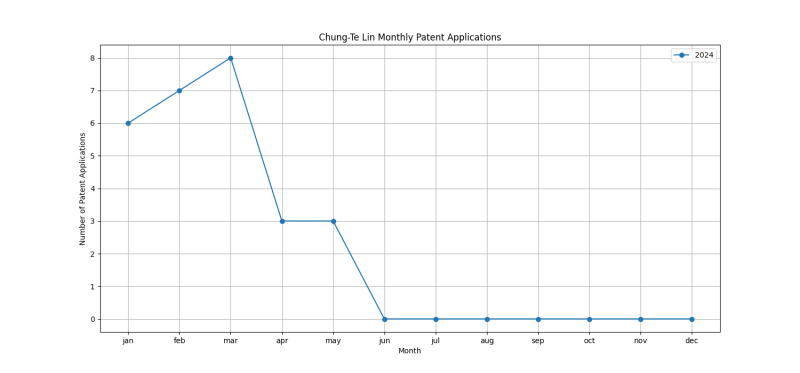

Patent Filing Activity

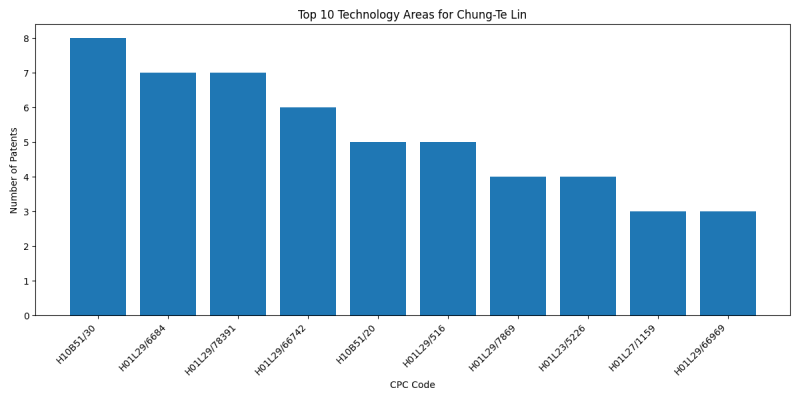

Technology Areas

List of Technology Areas

- H10B51/30 (ELECTRONIC MEMORY DEVICES): 8 patents

- H01L29/6684 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 7 patents

- H01L29/78391 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 7 patents

- H01L29/66742 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 6 patents

- H10B51/20 (ELECTRONIC MEMORY DEVICES): 5 patents

- H01L29/516 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 5 patents

- H01L29/7869 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 4 patents

- H01L23/5226 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 4 patents

- H01L27/1159 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 3 patents

- H01L29/66969 ({of devices having semiconductor bodies not comprising group 14 or group 13/15 materials (comprising selenium or tellurium in uncombined form other than as impurities in semiconductor bodies of other materials, comprising cuprous oxide or cuprous iodide): 3 patents

- H01L27/11597 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 3 patents

- H01L29/78696 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L29/401 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H10B51/10 (ELECTRONIC MEMORY DEVICES): 2 patents

- H10B51/40 (ELECTRONIC MEMORY DEVICES): 2 patents

- H10B53/30 (ELECTRONIC MEMORY DEVICES): 2 patents

- H01L23/5283 ({Geometry or} layout of the interconnection structure {(): 2 patents

- H01L29/0847 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H10B51/00 (Ferroelectric RAM [FeRAM] devices comprising ferroelectric memory transistors): 2 patents

- H01L27/11587 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L27/1207 ({combined with devices in contact with the semiconductor body, i.e. bulk/SOI hybrid circuits}): 2 patents

- H01L29/41733 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L29/42384 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L21/76876 ({Thin films associated with contacts of capacitors}): 1 patents

- H01L27/11514 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H10B53/20 (ELECTRONIC MEMORY DEVICES): 1 patents

- H01L21/02178 ({the material being a silicon nitride not containing oxygen, e.g. SixNy or SixByNz (): 1 patents

- H01L21/02194 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L21/0228 ({deposition by cyclic CVD, e.g. ALD, ALE, pulsed CVD}): 1 patents

- H10B20/20 (Programmable ROM [PROM] devices comprising field-effect components (): 1 patents

- G11C17/18 (Auxiliary circuits, e.g. for writing into memory): 1 patents

- G11C17/16 (using electrically-fusible links): 1 patents

- H01L28/75 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2924/1441 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L29/78642 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L27/124 (the substrate being other than a semiconductor body, e.g. an insulating body): 1 patents

- H01L27/127 (the substrate being other than a semiconductor body, e.g. an insulating body): 1 patents

- H01L27/1225 (the substrate being other than a semiconductor body, e.g. an insulating body): 1 patents

- H01L27/1255 (the substrate being other than a semiconductor body, e.g. an insulating body): 1 patents

- H10B41/23 (ELECTRONIC MEMORY DEVICES): 1 patents

- H10B41/27 (ELECTRONIC MEMORY DEVICES): 1 patents

- H10B41/35 (ELECTRONIC MEMORY DEVICES): 1 patents

- H10B43/23 (ELECTRONIC MEMORY DEVICES): 1 patents

- H10B51/50 (ELECTRONIC MEMORY DEVICES): 1 patents

- H01L21/84 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H10N50/01 (No explanation available): 1 patents

- G11C11/161 (using elements in which the storage effect is based on magnetic spin effect): 1 patents

- H01L21/76832 ({Multiple layers}): 1 patents

- H01L21/7684 (Applying interconnections to be used for carrying current between separate components within a device {comprising conductors and dielectrics}): 1 patents

- H01L21/76879 ({by selective deposition of conductive material in the vias, e.g. selective C.V.D. on semiconductor material, plating (plating on semiconductors in general): 1 patents

- H10B61/00 (Magnetic memory devices, e.g. magnetoresistive RAM [MRAM] devices): 1 patents

- H10N50/80 (No explanation available): 1 patents

- H10N50/85 (No explanation available): 1 patents

- H01L23/5381 (the interconnection structure between a plurality of semiconductor chips being formed on, or in, insulating substrates ({): 1 patents

- H01L21/4853 (Manufacture or treatment of parts, e.g. containers, prior to assembly of the devices, using processes not provided for in a single one of the subgroups): 1 patents

- H01L21/4857 (Manufacture or treatment of parts, e.g. containers, prior to assembly of the devices, using processes not provided for in a single one of the subgroups): 1 patents

- H01L21/486 (Manufacture or treatment of parts, e.g. containers, prior to assembly of the devices, using processes not provided for in a single one of the subgroups): 1 patents

- H01L23/49816 (Leads, {i.e. metallisations or lead-frames} on insulating substrates, {e.g. chip carriers (shape of the substrate): 1 patents

- H01L23/49822 ({Multilayer substrates (multilayer metallisation on monolayer substrate): 1 patents

- H01L23/49833 (Leads, {i.e. metallisations or lead-frames} on insulating substrates, {e.g. chip carriers (shape of the substrate): 1 patents

- H01L23/49838 (Leads, {i.e. metallisations or lead-frames} on insulating substrates, {e.g. chip carriers (shape of the substrate): 1 patents

- H01L23/5385 (the interconnection structure between a plurality of semiconductor chips being formed on, or in, insulating substrates ({): 1 patents

- H01L23/5386 (the interconnection structure between a plurality of semiconductor chips being formed on, or in, insulating substrates ({): 1 patents

- H01L24/16 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L25/162 (the devices being of types provided for in two or more different main groups of groups): 1 patents

- H01L2224/16225 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2924/1431 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2924/1436 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2924/1443 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L29/408 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L29/78648 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L29/4908 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L29/78603 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L27/0705 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H10B43/35 (ELECTRONIC MEMORY DEVICES): 1 patents

- H10B43/10 (ELECTRONIC MEMORY DEVICES): 1 patents

- H10B43/20 (ELECTRONIC MEMORY DEVICES): 1 patents

- H01L2924/1438 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2924/145 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- G11C11/223 ({using MOS with ferroelectric gate insulating film}): 1 patents

- G11C11/2275 ({Writing or programming circuits or methods}): 1 patents

- H01L27/11568 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L27/11521 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L27/228 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L27/2436 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- G11C16/08 (Address circuits; Decoders; Word-line control circuits): 1 patents

- G11C11/2257 ({Word-line or row circuits}): 1 patents

- G11C11/1657 ({Word-line or row circuits}): 1 patents

- G11C13/0028 ({Word-line or row circuits}): 1 patents

Companies

List of Companies

- Taiwan Semiconductor Manufacturing Company, Ltd.: 27 patents

Collaborators

- Hai-Ching Chen (11 collaborations)

- Yu-Ming Lin (8 collaborations)

- Wu-Wei Tsai (6 collaborations)

- Sheng-Chih Lai (6 collaborations)

- Feng-Cheng Yang (5 collaborations)

- Po-Ting Lin (4 collaborations)

- Yu-Ming Hsiang (4 collaborations)

- Yan-Yi Chen (4 collaborations)

- Kuo-Chang Chiang (4 collaborations)

- Song-Fu Liao (3 collaborations)

- Yu-Wei Jiang (3 collaborations)

- Chien-Hua Huang (2 collaborations)

- Chia-Yu Ling (2 collaborations)

- Kai-Wen Cheng (2 collaborations)

- Sai-Hooi Yeong (2 collaborations)

- Han-Ting Tsai (2 collaborations)

- Ya-Ling Lee (2 collaborations)

- Wei-Chih Wen (2 collaborations)

- Katherine H CHIANG (2 collaborations)

- Pin-Cheng Hsu (2 collaborations)

- Yen-Chieh Huang (2 collaborations)

- Chieh-Fang Chen (2 collaborations)

- Chen-Jun Wu (2 collaborations)

- Yi-Cheng Chu (1 collaborations)

- Katherine H. CHIANG (1 collaborations)

- Rainer Yen-Chieh Huang (1 collaborations)

- Chien-Hao Huang (1 collaborations)

- Gao-Ming Wu (1 collaborations)

- Wei-Gang Chiu (1 collaborations)

- Ming-Yi Yang (1 collaborations)

- Yin-Hao Wu (1 collaborations)

- Yu-Chuan Shih (1 collaborations)

- Chun-Chieh Lu (1 collaborations)

- Neil Quinn Murray (1 collaborations)

- Katherine H. Chiang (1 collaborations)

- Yen-Chung Ho (1 collaborations)

- Yu-Feng Yin (1 collaborations)

- Min-Kun Dai (1 collaborations)

- Hsin-Yu LAI (1 collaborations)

- Hung-Chang Sun (1 collaborations)

- TsuChing Yang (1 collaborations)

- Wen-Ling Lu (1 collaborations)

- Ya-Yun Cheng (1 collaborations)

- Yi-Ching Liu (1 collaborations)

- Sun-Yi Chang (1 collaborations)

Subcategories

This category has the following 3 subcategories, out of 3 total.

Categories:

- Hai-Ching Chen

- Yu-Ming Lin

- Wu-Wei Tsai

- Sheng-Chih Lai

- Feng-Cheng Yang

- Po-Ting Lin

- Yu-Ming Hsiang

- Yan-Yi Chen

- Kuo-Chang Chiang

- Song-Fu Liao

- Yu-Wei Jiang

- Chien-Hua Huang

- Chia-Yu Ling

- Kai-Wen Cheng

- Sai-Hooi Yeong

- Han-Ting Tsai

- Ya-Ling Lee

- Wei-Chih Wen

- Katherine H CHIANG

- Pin-Cheng Hsu

- Yen-Chieh Huang

- Chieh-Fang Chen

- Chen-Jun Wu

- Yi-Cheng Chu

- Katherine H. CHIANG

- Rainer Yen-Chieh Huang

- Chien-Hao Huang

- Gao-Ming Wu

- Wei-Gang Chiu

- Ming-Yi Yang

- Yin-Hao Wu

- Yu-Chuan Shih

- Chun-Chieh Lu

- Neil Quinn Murray

- Katherine H. Chiang

- Yen-Chung Ho

- Yu-Feng Yin

- Min-Kun Dai

- Hsin-Yu LAI

- Hung-Chang Sun

- TsuChing Yang

- Wen-Ling Lu

- Ya-Yun Cheng

- Yi-Ching Liu

- Sun-Yi Chang

- Chung-Te Lin

- Inventors

- Inventors filing patents with Taiwan Semiconductor Manufacturing Company, Ltd.