Category:Chih-Hao Wang

Jump to navigation

Jump to search

Contents

Chih-Hao Wang

Executive Summary

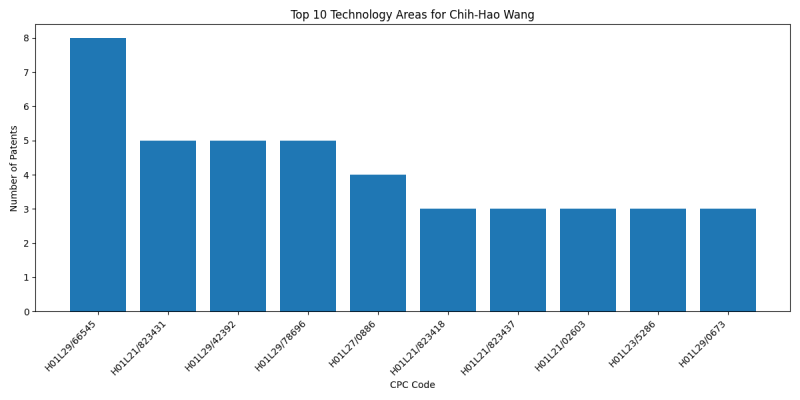

Chih-Hao Wang is an inventor who has filed 13 patents. Their primary areas of innovation include {using a dummy, i.e. replacement gate in a process wherein at least a part of the final gate is self aligned to the dummy gate} (8 patents), to produce devices, e.g. integrated circuits, each consisting of a plurality of components (5 patents), SEMICONDUCTOR DEVICES NOT COVERED BY CLASS (5 patents), and they have worked with companies such as Taiwan Semiconductor Manufacturing Co., Ltd. (13 patents). Their most frequent collaborators include (5 collaborations), (5 collaborations), (4 collaborations).

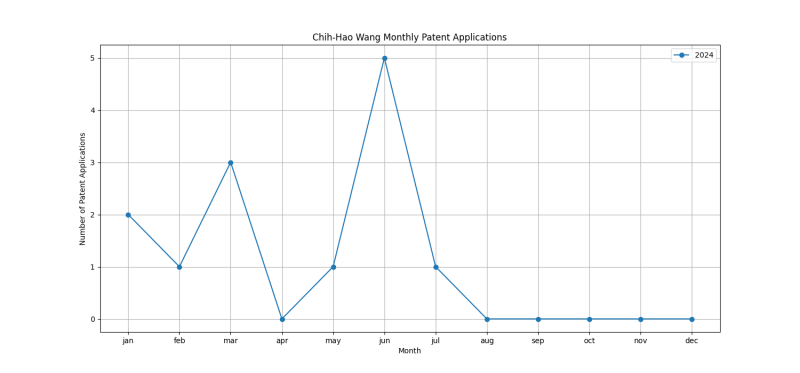

Patent Filing Activity

Technology Areas

List of Technology Areas

- H01L29/66545 ({using a dummy, i.e. replacement gate in a process wherein at least a part of the final gate is self aligned to the dummy gate}): 8 patents

- H01L21/823431 (to produce devices, e.g. integrated circuits, each consisting of a plurality of components): 5 patents

- H01L29/42392 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 5 patents

- H01L29/78696 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 5 patents

- H01L27/0886 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 4 patents

- H01L21/823418 (to produce devices, e.g. integrated circuits, each consisting of a plurality of components): 3 patents

- H01L21/823437 (to produce devices, e.g. integrated circuits, each consisting of a plurality of components): 3 patents

- H01L21/02603 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 3 patents

- H01L23/5286 ({Geometry or} layout of the interconnection structure {(): 3 patents

- H01L29/0673 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 3 patents

- H01L29/41733 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 3 patents

- H01L29/66553 ({using self aligned silicidation, i.e. salicide (formation of conductive layers comprising silicides): 3 patents

- H01L29/66742 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 3 patents

- H01L29/78618 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 3 patents

- H01L21/0337 ({characterised by the process involved to create the mask, e.g. lift-off masks, sidewalls, or to modify the mask, e.g. pre-treatment, post-treatment}): 2 patents

- H01L29/0649 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L29/785 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L29/66636 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L29/7848 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L21/823412 (to produce devices, e.g. integrated circuits, each consisting of a plurality of components): 2 patents

- H01L21/823481 (to produce devices, e.g. integrated circuits, each consisting of a plurality of components): 2 patents

- H01L29/0653 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L29/0847 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L27/0924 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L29/66795 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L29/7851 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L29/6656 ({using self aligned silicidation, i.e. salicide (formation of conductive layers comprising silicides): 2 patents

- H01L21/02532 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L21/30604 (Chemical or electrical treatment, e.g. electrolytic etching (to form insulating layers): 2 patents

- H01L29/45 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L27/092 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L21/823468 (to produce devices, e.g. integrated circuits, each consisting of a plurality of components): 1 patents

- H01L21/7682 (Applying interconnections to be used for carrying current between separate components within a device {comprising conductors and dielectrics}): 1 patents

- H01L21/76805 ({the opening being a via or contact hole penetrating the underlying conductor}): 1 patents

- H01L21/76895 (Applying interconnections to be used for carrying current between separate components within a device {comprising conductors and dielectrics}): 1 patents

- H01L23/5329 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L21/823475 (to produce devices, e.g. integrated circuits, each consisting of a plurality of components): 1 patents

- H01L23/535 (including internal interconnections, e.g. cross-under constructions {(internal lead connections): 1 patents

- H01L29/1037 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L29/6681 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L29/161 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L29/165 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L23/481 (Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements {; Selection of materials therefor}): 1 patents

- H01L23/53295 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L29/66507 ({providing different silicide thicknesses on the gate and on source or drain}): 1 patents

- H01L21/76832 ({Multiple layers}): 1 patents

- H01L21/76834 ({formation of thin insulating films on the sidewalls or on top of conductors (): 1 patents

- H01L21/02576 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L21/02579 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L21/31111 ({by chemical means}): 1 patents

- H01L21/76897 ({Formation of self-aligned vias or contact plugs, i.e. involving a lithographically uncritical step (self-aligned silicidation on field effect transistors): 1 patents

- H01L21/823871 (to produce devices, e.g. integrated circuits, each consisting of a plurality of components): 1 patents

- H01L21/28518 (from a gas or vapour, e.g. condensation): 1 patents

- H01L21/823807 (to produce devices, e.g. integrated circuits, each consisting of a plurality of components): 1 patents

- H01L21/823814 (to produce devices, e.g. integrated circuits, each consisting of a plurality of components): 1 patents

- H01L29/0665 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L29/66818 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L29/516 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L21/0206 ({during, before or after processing of insulating layers}): 1 patents

- H01L21/823828 (to produce devices, e.g. integrated circuits, each consisting of a plurality of components): 1 patents

- H01L21/823857 (to produce devices, e.g. integrated circuits, each consisting of a plurality of components): 1 patents

- H01L29/42364 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L29/513 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L29/517 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L29/6684 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L29/78391 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L21/0262 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L29/401 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L29/6653 ({using self aligned silicidation, i.e. salicide (formation of conductive layers comprising silicides): 1 patents

Companies

List of Companies

- Taiwan Semiconductor Manufacturing Co., Ltd.: 13 patents

Collaborators

- Kuan-Lun Cheng (5 collaborations)

- Kuo-Cheng Chiang (5 collaborations)

- Huan-Chieh Su (4 collaborations)

- Cheng-Chi Chuang (4 collaborations)

- Zhi-Chang Lin (3 collaborations)

- Li-Zhen Yu (3 collaborations)

- Lin-Yu Huang (3 collaborations)

- Shi Ning Ju (3 collaborations)

- Kuo-Cheng Ching (2 collaborations)

- Chia-Hao Chang (2 collaborations)

- Jia-Ni Yu (2 collaborations)

- Guan-Lin Chen (2 collaborations)

- Kuo-Cheng CHING (1 collaborations)

- Chun-Yuan Chen (1 collaborations)

- Yu-Ming Lin (1 collaborations)

- Lung-Kun Chu (1 collaborations)

- Mao-Lin Huang (1 collaborations)

- Chung-Wei Hsu (1 collaborations)

- Chih-Chao Chou (1 collaborations)

- Wen-Ting Lan (1 collaborations)

- Jui-Chien Huang (1 collaborations)

- Shih-Cheng Chen (1 collaborations)

- Jung-Hung Chang (1 collaborations)

- Lo-Heng Chang (1 collaborations)

- Jia-Chuan You (1 collaborations)

- Min Cao (1 collaborations)

- Pei-Yu Wang (1 collaborations)

- Sai-Hooi Yeong (1 collaborations)

- Ching-Wei Tsai (1 collaborations)

- Wei-Hao Wu (1 collaborations)

Subcategories

This category has the following 5 subcategories, out of 5 total.

C

K

S

Y

Categories:

- Kuan-Lun Cheng

- Kuo-Cheng Chiang

- Huan-Chieh Su

- Cheng-Chi Chuang

- Zhi-Chang Lin

- Li-Zhen Yu

- Lin-Yu Huang

- Shi Ning Ju

- Kuo-Cheng Ching

- Chia-Hao Chang

- Jia-Ni Yu

- Guan-Lin Chen

- Kuo-Cheng CHING

- Chun-Yuan Chen

- Yu-Ming Lin

- Lung-Kun Chu

- Mao-Lin Huang

- Chung-Wei Hsu

- Chih-Chao Chou

- Wen-Ting Lan

- Jui-Chien Huang

- Shih-Cheng Chen

- Jung-Hung Chang

- Lo-Heng Chang

- Jia-Chuan You

- Min Cao

- Pei-Yu Wang

- Sai-Hooi Yeong

- Ching-Wei Tsai

- Wei-Hao Wu

- Chih-Hao Wang

- Inventors

- Inventors filing patents with Taiwan Semiconductor Manufacturing Co., Ltd.