NVIDIA Patent Application Trends in 2024: Difference between revisions

Appearance

No edit summary |

No edit summary |

||

| Line 1: | Line 1: | ||

== NVIDIA Patent Filing Activity == | == NVIDIA Patent Filing Activity == | ||

=== 2024 === | === 2024 === | ||

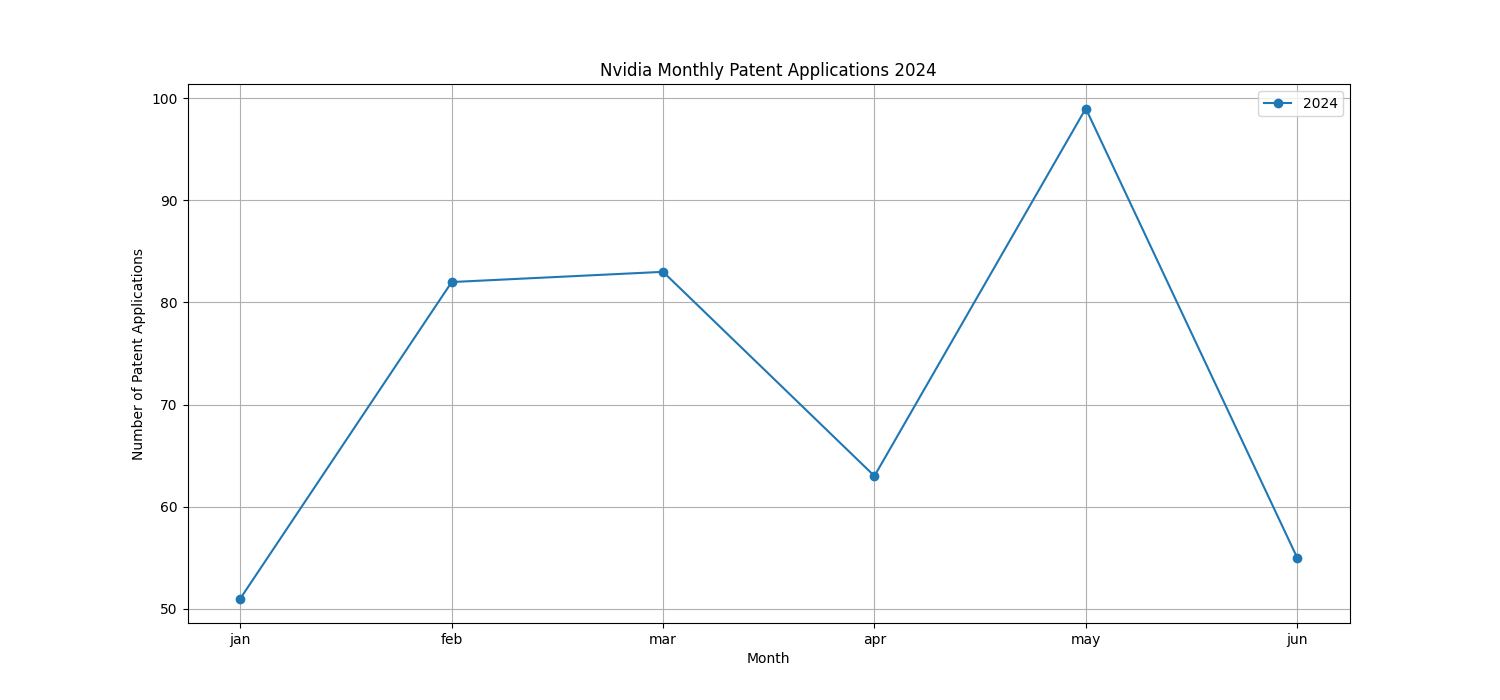

[[File:Nvidia | [[File:Nvidia Monthly Patent Applications 2024 - Up to June 2024.png|800px|frame]] | ||

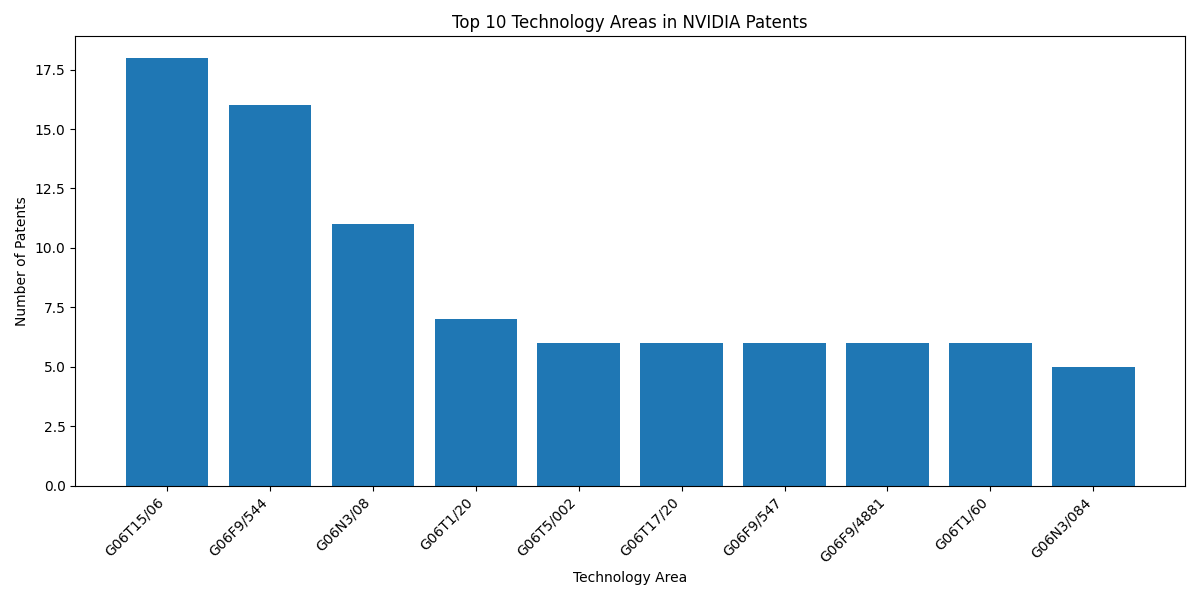

== Top 10 | == Top 10 Technology Areas == | ||

[[File:Nvidia | [[File:Nvidia Top Technology Areas 2024 - Up to 11 July 2024.png|800px|frame|Nvidia Top Technology Areas 2024 - Up to 11 July 2024]] | ||

* [[:Category:CPC_G06T15_06| | * [[:Category:CPC_G06T15_06|G06T15/06]]: 18 patents | ||

* [[:Category:CPC_G06F9_544| | ** Example: EARLY RELEASE OF RESOURCES IN RAY TRACING HARDWARE | ||

* [[:Category:CPC_G06N3_08| | * [[:Category:CPC_G06F9_544|G06F9/544]]: 16 patents | ||

* [[:Category:CPC_G06T1_20| | ** Example: APPLICATION PROGRAMMING INTERFACE TO INDICATE STORAGE OF ACCELERATOR ERRORS | ||

* [[:Category:CPC_G06T5_002| | * [[:Category:CPC_G06N3_08|G06N3/08]]: 11 patents | ||

* [[:Category:CPC_G06T17_20| | ** Example: DISTANCE TO OBSTACLE DETECTION IN AUTONOMOUS MACHINE APPLICATIONS | ||

* [[:Category:CPC_G06F9_547| | * [[:Category:CPC_G06T1_20|G06T1/20]]: 7 patents | ||

* [[:Category:CPC_G06F9_4881| | ** Example: FRACTIONALIZED TRANSFERS OF SENSOR DATA FOR STREAMING AND LATENCY-SENSITIVE APPLICATIONS | ||

* [[:Category:CPC_G06T1_60| | * [[:Category:CPC_G06T5_002|G06T5/002]]: 6 patents | ||

* [[:Category:CPC_G06N3_084| | ** Example: NEURAL NETWORK-BASED PERTURBATION REMOVAL | ||

* [[:Category:CPC_G06T17_20|G06T17/20]]: 6 patents | |||

** Example: MESH TOPOLOGY GENERATION USING PARALLEL PROCESSING | |||

* [[:Category:CPC_G06F9_547|G06F9/547]]: 6 patents | |||

** Example: APPLICATION PROGRAMMING INTERFACE TO INDICATE A CONTROLLER TO A DEVICE IN AN ACCESS NETWORK | |||

* [[:Category:CPC_G06F9_4881|G06F9/4881]]: 6 patents | |||

** Example: GRAPH MODIFICATION | |||

* [[:Category:CPC_G06T1_60|G06T1/60]]: 6 patents | |||

** Example: APPLICATION PROGRAMMING INTERFACE TO INDICATE MEMORY TRANSACTION | |||

* [[:Category:CPC_G06N3_084|G06N3/084]]: 5 patents | |||

** Example: ANNOTATING HIGH DEFINITION MAP DATA WITH SEMANTIC LABELS | |||

== Emerging | == Emerging Technology Areas == | ||

* [[:Category:CPC_G01C21_26| | [[File:Nvidia Top Emerging Technology Areas 2024 - Up to 11 July 2024.png|800px|frame|Nvidia Top Emerging Technology Areas 2024 - Up to 11 July 2024]] | ||

* [[:Category:CPC_G06F3_0613| | * [[:Category:CPC_G01C21_26|G01C21/26]]: 1 patents | ||

* [[:Category:CPC_G06F9_3824| | ** Example: INTERSECTION POSE DETECTION IN AUTONOMOUS MACHINE APPLICATIONS | ||

* [[:Category:CPC_G06F9_5038| | * [[:Category:CPC_G06F3_0613|G06F3/0613]]: 1 patents | ||

* [[:Category:CPC_G06F11_3409| | ** Example: HARDWARE LATENCY MONITORING FOR MEMORY DEVICE INPUT/OUTPUT REQUESTS | ||

* [[:Category:CPC_G06F11_3644| | * [[:Category:CPC_G06F9_3824|G06F9/3824]]: 1 patents | ||

* [[:Category:CPC_G06T7_30| | ** Example: WORKLOAD ASSIGNMENT TECHNIQUE | ||

* [[:Category:CPC_G06V10_56| | * [[:Category:CPC_G06F9_5038|G06F9/5038]]: 1 patents | ||

* [[:Category:CPC_G06V20_54| | ** Example: TECHNIQUES FOR BALANCING DYNAMIC INFERENCING BY MACHINE LEARNING MODELS | ||

* [[:Category:CPC_H03K19_1776| | * [[:Category:CPC_G06F11_3409|G06F11/3409]]: 1 patents | ||

** Example: APPLICATION EXECUTION ALLOCATION USING MACHINE LEARNING | |||

* [[:Category:CPC_G06F11_3644|G06F11/3644]]: 1 patents | |||

** Example: SOFTWARE PROGRAM ERROR TESTING FOR AUTONOMOUS SYSTEMS AND APPLICATIONS | |||

* [[:Category:CPC_G06T7_30|G06T7/30]]: 1 patents | |||

** Example: IMAGE PROCESSING USING NEURAL NETWORKS, WITH IMAGE REGISTRATION | |||

* [[:Category:CPC_G06V10_56|G06V10/56]]: 1 patents | |||

** Example: REMOVING ARTIFACTS USING DITHERING COMPENSATION IN IMAGE STREAMING SYSTEMS AND APPLICATIONS | |||

* [[:Category:CPC_G06V20_54|G06V20/54]]: 1 patents | |||

** Example: SCENARIO RECREATION THROUGH OBJECT DETECTION AND 3D VISUALIZATION IN A MULTI-SENSOR ENVIRONMENT | |||

* [[:Category:CPC_H03K19_1776|H03K19/1776]]: 1 patents | |||

** Example: DIGITALLY CONTROLLED UNIFIED RECEIVER FOR MULTI-RANK SYSTEM | |||

Revision as of 08:47, 11 July 2024

NVIDIA Patent Filing Activity

2024

Top 10 Technology Areas

- G06T15/06: 18 patents

- Example: EARLY RELEASE OF RESOURCES IN RAY TRACING HARDWARE

- G06F9/544: 16 patents

- Example: APPLICATION PROGRAMMING INTERFACE TO INDICATE STORAGE OF ACCELERATOR ERRORS

- G06N3/08: 11 patents

- Example: DISTANCE TO OBSTACLE DETECTION IN AUTONOMOUS MACHINE APPLICATIONS

- G06T1/20: 7 patents

- Example: FRACTIONALIZED TRANSFERS OF SENSOR DATA FOR STREAMING AND LATENCY-SENSITIVE APPLICATIONS

- G06T5/002: 6 patents

- Example: NEURAL NETWORK-BASED PERTURBATION REMOVAL

- G06T17/20: 6 patents

- Example: MESH TOPOLOGY GENERATION USING PARALLEL PROCESSING

- G06F9/547: 6 patents

- Example: APPLICATION PROGRAMMING INTERFACE TO INDICATE A CONTROLLER TO A DEVICE IN AN ACCESS NETWORK

- G06F9/4881: 6 patents

- Example: GRAPH MODIFICATION

- G06T1/60: 6 patents

- Example: APPLICATION PROGRAMMING INTERFACE TO INDICATE MEMORY TRANSACTION

- G06N3/084: 5 patents

- Example: ANNOTATING HIGH DEFINITION MAP DATA WITH SEMANTIC LABELS

Emerging Technology Areas

- G01C21/26: 1 patents

- Example: INTERSECTION POSE DETECTION IN AUTONOMOUS MACHINE APPLICATIONS

- G06F3/0613: 1 patents

- Example: HARDWARE LATENCY MONITORING FOR MEMORY DEVICE INPUT/OUTPUT REQUESTS

- G06F9/3824: 1 patents

- Example: WORKLOAD ASSIGNMENT TECHNIQUE

- G06F9/5038: 1 patents

- Example: TECHNIQUES FOR BALANCING DYNAMIC INFERENCING BY MACHINE LEARNING MODELS

- G06F11/3409: 1 patents

- Example: APPLICATION EXECUTION ALLOCATION USING MACHINE LEARNING

- G06F11/3644: 1 patents

- Example: SOFTWARE PROGRAM ERROR TESTING FOR AUTONOMOUS SYSTEMS AND APPLICATIONS

- G06T7/30: 1 patents

- Example: IMAGE PROCESSING USING NEURAL NETWORKS, WITH IMAGE REGISTRATION

- G06V10/56: 1 patents

- Example: REMOVING ARTIFACTS USING DITHERING COMPENSATION IN IMAGE STREAMING SYSTEMS AND APPLICATIONS

- G06V20/54: 1 patents

- Example: SCENARIO RECREATION THROUGH OBJECT DETECTION AND 3D VISUALIZATION IN A MULTI-SENSOR ENVIRONMENT

- H03K19/1776: 1 patents

- Example: DIGITALLY CONTROLLED UNIFIED RECEIVER FOR MULTI-RANK SYSTEM