Difference between revisions of "Category:Hsien-Wei Chen"

Wikipatents (talk | contribs) (Updating Category:Hsien-Wei_Chen) |

Wikipatents (talk | contribs) (Updating Category:Hsien-Wei_Chen) |

||

| Line 2: | Line 2: | ||

=== Executive Summary === | === Executive Summary === | ||

| − | Hsien-Wei Chen is an inventor who has filed | + | Hsien-Wei Chen is an inventor who has filed 9 patents. Their primary areas of innovation include {Multistep manufacturing processes of assemblies consisting of devices, each device being of a type provided for in group (5 patents), {Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected} (4 patents), SEMICONDUCTOR DEVICES NOT COVERED BY CLASS (4 patents), and they have worked with companies such as Taiwan Semiconductor Manufacturing Co., Ltd. (8 patents), Taiwan Semiconductor Manufacturing CO., Ltd. (1 patents). Their most frequent collaborators include [[Category:Ming-Fa Chen|Ming-Fa Chen]] (6 collaborations), [[Category:Shin-Puu Jeng|Shin-Puu Jeng]] (3 collaborations), [[Category:Jie Chen|Jie Chen]] (3 collaborations). |

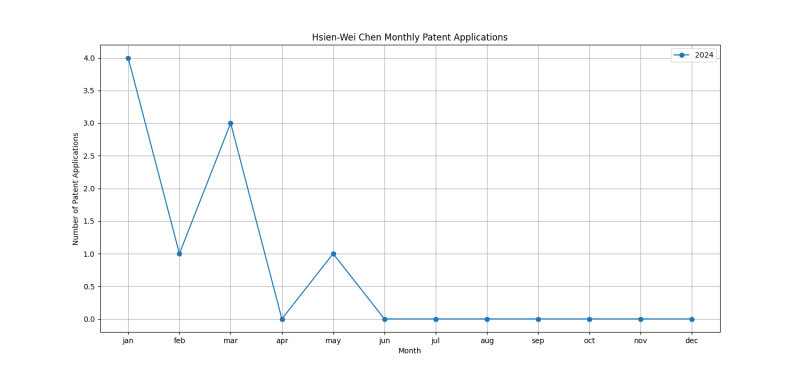

=== Patent Filing Activity === | === Patent Filing Activity === | ||

| Line 11: | Line 11: | ||

==== List of Technology Areas ==== | ==== List of Technology Areas ==== | ||

| − | * [[:Category:CPC_H01L23/49838|H01L23/49838]] ( | + | * [[:Category:CPC_H01L25/50|H01L25/50]] ({Multistep manufacturing processes of assemblies consisting of devices, each device being of a type provided for in group): 5 patents |

| − | * [[:Category: | + | * [[:Category:CPC_H01L24/80|H01L24/80]] ({Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected}): 4 patents |

| − | * [[:Category: | + | * [[:Category:CPC_H01L25/0657|H01L25/0657]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 4 patents |

| − | * [[:Category: | + | * [[:Category:CPC_H01L24/08|H01L24/08]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 3 patents |

| − | * [[:Category:CPC_H01L23/585|H01L23/585]] ( | + | * [[:Category:CPC_H01L25/18|H01L25/18]] (the devices being of types provided for in two or more different subgroups of the same main group of groups): 3 patents |

| − | * [[:Category:CPC_H01L21/ | + | * [[:Category:CPC_H01L2224/80895|H01L2224/80895]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 3 patents |

| − | * [[:Category:CPC_H01L23/ | + | * [[:Category:CPC_H01L2224/80896|H01L2224/80896]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 3 patents |

| − | * [[:Category:CPC_H01L24/ | + | * [[:Category:CPC_H01L21/4853|H01L21/4853]] (Manufacture or treatment of parts, e.g. containers, prior to assembly of the devices, using processes not provided for in a single one of the subgroups): 2 patents |

| − | * [[:Category: | + | * [[:Category:CPC_H01L21/4857|H01L21/4857]] (Manufacture or treatment of parts, e.g. containers, prior to assembly of the devices, using processes not provided for in a single one of the subgroups): 2 patents |

| − | * [[:Category:CPC_H01L23/ | + | * [[:Category:CPC_H01L23/49816|H01L23/49816]] (Leads, {i.e. metallisations or lead-frames} on insulating substrates, {e.g. chip carriers (shape of the substrate): 2 patents |

| − | * [[:Category:CPC_H01L23/ | + | * [[:Category:CPC_H01L23/49822|H01L23/49822]] ({Multilayer substrates (multilayer metallisation on monolayer substrate): 2 patents |

| − | * [[:Category: | + | * [[:Category:CPC_H01L23/49833|H01L23/49833]] (Leads, {i.e. metallisations or lead-frames} on insulating substrates, {e.g. chip carriers (shape of the substrate): 2 patents |

| − | * [[:Category: | + | * [[:Category:CPC_H01L23/49838|H01L23/49838]] (Leads, {i.e. metallisations or lead-frames} on insulating substrates, {e.g. chip carriers (shape of the substrate): 2 patents |

| − | * [[:Category:CPC_H01L21/ | + | * [[:Category:CPC_H01L24/16|H01L24/16]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents |

| + | * [[:Category:CPC_H01L24/32|H01L24/32]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents | ||

| + | * [[:Category:CPC_H01L24/73|H01L24/73]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents | ||

| + | * [[:Category:CPC_H01L2224/16238|H01L2224/16238]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents | ||

| + | * [[:Category:CPC_H01L2224/32225|H01L2224/32225]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents | ||

| + | * [[:Category:CPC_H01L2924/15311|H01L2924/15311]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents | ||

| + | * [[:Category:CPC_H01L24/09|H01L24/09]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents | ||

| + | * [[:Category:CPC_H01L2225/06541|H01L2225/06541]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents | ||

| + | * [[:Category:CPC_H01L2924/1431|H01L2924/1431]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents | ||

| + | * [[:Category:CPC_H01L23/3128|H01L23/3128]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents | ||

| + | * [[:Category:CPC_H01L23/481|H01L23/481]] (Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements {; Selection of materials therefor}): 2 patents | ||

| + | * [[:Category:CPC_H01L25/105|H01L25/105]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents | ||

| + | * [[:Category:CPC_H01L2225/1035|H01L2225/1035]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents | ||

| + | * [[:Category:CPC_H01L2225/1041|H01L2225/1041]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents | ||

| + | * [[:Category:CPC_H01L2225/1058|H01L2225/1058]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents | ||

| + | * [[:Category:CPC_H01L23/66|H01L23/66]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L21/486|H01L21/486]] (Manufacture or treatment of parts, e.g. containers, prior to assembly of the devices, using processes not provided for in a single one of the subgroups): 1 patents | ||

| + | * [[:Category:CPC_H01L23/552|H01L23/552]] (Protection against radiation, e.g. light {or electromagnetic waves}): 1 patents | ||

| + | * [[:Category:CPC_H01L24/96|H01L24/96]] ({the devices being encapsulated in a common layer, e.g. neo-wafer or pseudo-wafer, said common layer being separable into individual assemblies after connecting}): 1 patents | ||

| + | * [[:Category:CPC_H01L24/97|H01L24/97]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H10B80/00|H10B80/00]] (Assemblies of multiple devices comprising at least one memory device covered by this subclass): 1 patents | ||

| + | * [[:Category:CPC_H01L2223/6616|H01L2223/6616]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L2223/6672|H01L2223/6672]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L2224/16227|H01L2224/16227]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L2224/73204|H01L2224/73204]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L2224/95001|H01L2224/95001]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L2224/96|H01L2224/96]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L2224/97|H01L2224/97]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L2924/15174|H01L2924/15174]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L23/585|H01L23/585]] ({comprising conductive layers or plates or strips or rods or rings (): 1 patents | ||

| + | * [[:Category:CPC_H01L23/5226|H01L23/5226]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L23/53295|H01L23/53295]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L29/0649|H01L29/0649]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L24/83|H01L24/83]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L24/03|H01L24/03]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L24/33|H01L24/33]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L23/562|H01L23/562]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L2225/06568|H01L2225/06568]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L2225/06565|H01L2225/06565]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L2225/06593|H01L2225/06593]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L2225/06513|H01L2225/06513]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L2225/06524|H01L2225/06524]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L2224/94|H01L2224/94]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L21/565|H01L21/565]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L25/0652|H01L25/0652]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L2924/1434|H01L2924/1434]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L2225/06589|H01L2225/06589]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L2225/06586|H01L2225/06586]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L2224/08145|H01L2224/08145]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L2225/06582|H01L2225/06582]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L2224/08146|H01L2224/08146]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L23/5385|H01L23/5385]] (the interconnection structure between a plurality of semiconductor chips being formed on, or in, insulating substrates ({): 1 patents | ||

| + | * [[:Category:CPC_H01L2224/08225|H01L2224/08225]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L23/3735|H01L23/3735]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L24/13|H01L24/13]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L24/81|H01L24/81]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L23/3185|H01L23/3185]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L2224/13111|H01L2224/13111]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L2224/13139|H01L2224/13139]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L2224/13147|H01L2224/13147]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L2224/81193|H01L2224/81193]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L2224/81815|H01L2224/81815]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L2924/1517|H01L2924/1517]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L2924/3511|H01L2924/3511]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L23/50|H01L23/50]] (for integrated circuit devices, {e.g. power bus, number of leads} (): 1 patents | ||

| + | * [[:Category:CPC_H01L23/5386|H01L23/5386]] (the interconnection structure between a plurality of semiconductor chips being formed on, or in, insulating substrates ({): 1 patents | ||

| + | * [[:Category:CPC_H01L23/5389|H01L23/5389]] (the interconnection structure between a plurality of semiconductor chips being formed on, or in, insulating substrates ({): 1 patents | ||

| + | * [[:Category:CPC_H01L24/17|H01L24/17]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L24/19|H01L24/19]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L24/20|H01L24/20]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L24/48|H01L24/48]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L2224/04042|H01L2224/04042]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L2224/04105|H01L2224/04105]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L2224/12105|H01L2224/12105]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L2224/48091|H01L2224/48091]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L2224/48227|H01L2224/48227]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L2224/73265|H01L2224/73265]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L2224/73267|H01L2224/73267]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L2224/81385|H01L2224/81385]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L2924/00014|H01L2924/00014]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L2924/14|H01L2924/14]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L2924/181|H01L2924/181]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L21/481|H01L21/481]] (Manufacture or treatment of parts, e.g. containers, prior to assembly of the devices, using processes not provided for in a single one of the subgroups): 1 patents | ||

| + | * [[:Category:CPC_H01L21/56|H01L21/56]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L25/0655|H01L25/0655]] (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents | ||

| + | * [[:Category:CPC_H01L24/06|H01L24/06]] ({of a plurality of bonding areas}): 1 patents | ||

| + | * [[:Category:CPC_H01L23/49503|H01L23/49503]] (Lead-frames {or other flat leads (): 1 patents | ||

| + | * [[:Category:CPC_H01L23/49827|H01L23/49827]] ({Via connections through the substrates, e.g. pins going through the substrate, coaxial cables (): 1 patents | ||

| + | * [[:Category:CPC_H03K19/1776|H03K19/1776]] (PULSE TECHNIQUE (measuring pulse characteristics): 1 patents | ||

=== Companies === | === Companies === | ||

| Line 30: | Line 118: | ||

==== List of Companies ==== | ==== List of Companies ==== | ||

| − | * Taiwan Semiconductor Manufacturing | + | * Taiwan Semiconductor Manufacturing Co., Ltd.: 8 patents |

| + | * Taiwan Semiconductor Manufacturing CO., Ltd.: 1 patents | ||

=== Collaborators === | === Collaborators === | ||

| + | * [[:Category:Ming-Fa Chen|Ming-Fa Chen]][[Category:Ming-Fa Chen]] (6 collaborations) | ||

| + | * [[:Category:Shin-Puu Jeng|Shin-Puu Jeng]][[Category:Shin-Puu Jeng]] (3 collaborations) | ||

| + | * [[:Category:Jie Chen|Jie Chen]][[Category:Jie Chen]] (3 collaborations) | ||

| + | * [[:Category:Chieh-Lung Lai|Chieh-Lung Lai]][[Category:Chieh-Lung Lai]] (2 collaborations) | ||

* [[:Category:Meng-Liang Lin|Meng-Liang Lin]][[Category:Meng-Liang Lin]] (2 collaborations) | * [[:Category:Meng-Liang Lin|Meng-Liang Lin]][[Category:Meng-Liang Lin]] (2 collaborations) | ||

| − | * [[:Category: | + | * [[:Category:Chih-Chia Hu|Chih-Chia Hu]][[Category:Chih-Chia Hu]] (2 collaborations) |

| − | * [[:Category:Chun | + | * [[:Category:Chen-Hua Yu|Chen-Hua Yu]][[Category:Chen-Hua Yu]] (2 collaborations) |

| + | * [[:Category:Chun-Yueh Yang|Chun-Yueh Yang]][[Category:Chun-Yueh Yang]] (1 collaborations) | ||

| + | * [[:Category:Chun-Chiang Kuo|Chun-Chiang Kuo]][[Category:Chun-Chiang Kuo]] (1 collaborations) | ||

| + | * [[:Category:Sen-Bor Jan|Sen-Bor Jan]][[Category:Sen-Bor Jan]] (1 collaborations) | ||

| + | * [[:Category:Ying-Ju Chen|Ying-Ju Chen]][[Category:Ying-Ju Chen]] (1 collaborations) | ||

| + | * [[:Category:Der-Chyang Yeh|Der-Chyang Yeh]][[Category:Der-Chyang Yeh]] (1 collaborations) | ||

[[Category:Hsien-Wei Chen]] | [[Category:Hsien-Wei Chen]] | ||

[[Category:Inventors]] | [[Category:Inventors]] | ||

| − | [[Category:Inventors filing patents with Taiwan Semiconductor Manufacturing | + | [[Category:Inventors filing patents with Taiwan Semiconductor Manufacturing Co., Ltd.]] |

| + | [[Category:Inventors filing patents with Taiwan Semiconductor Manufacturing CO., Ltd.]] | ||

Latest revision as of 06:48, 18 July 2024

Contents

Hsien-Wei Chen

Executive Summary

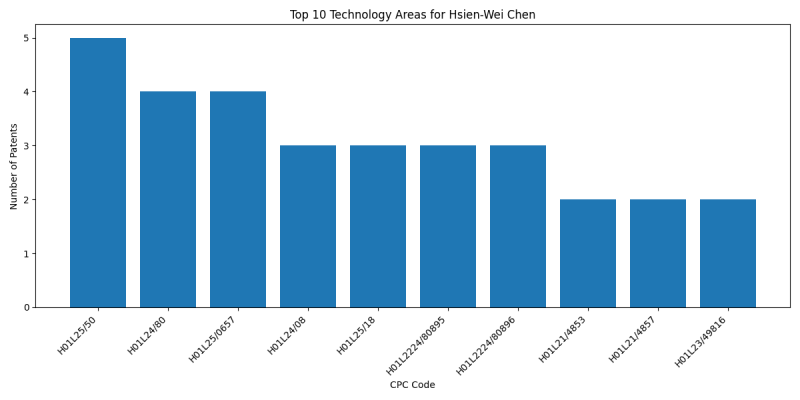

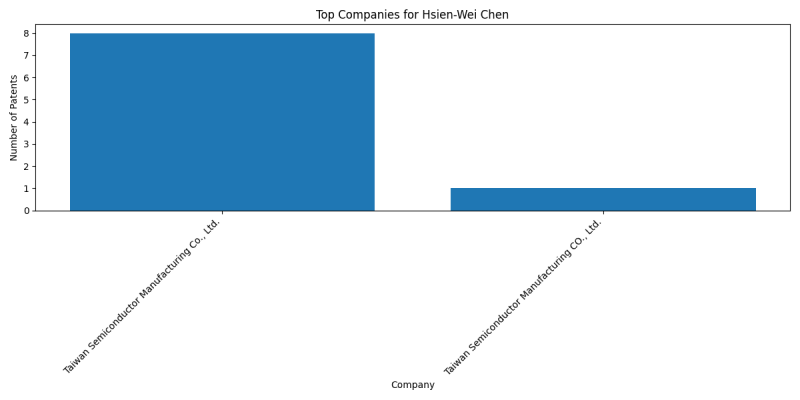

Hsien-Wei Chen is an inventor who has filed 9 patents. Their primary areas of innovation include {Multistep manufacturing processes of assemblies consisting of devices, each device being of a type provided for in group (5 patents), {Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected} (4 patents), SEMICONDUCTOR DEVICES NOT COVERED BY CLASS (4 patents), and they have worked with companies such as Taiwan Semiconductor Manufacturing Co., Ltd. (8 patents), Taiwan Semiconductor Manufacturing CO., Ltd. (1 patents). Their most frequent collaborators include (6 collaborations), (3 collaborations), (3 collaborations).

Patent Filing Activity

Technology Areas

List of Technology Areas

- H01L25/50 ({Multistep manufacturing processes of assemblies consisting of devices, each device being of a type provided for in group): 5 patents

- H01L24/80 ({Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected}): 4 patents

- H01L25/0657 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 4 patents

- H01L24/08 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 3 patents

- H01L25/18 (the devices being of types provided for in two or more different subgroups of the same main group of groups): 3 patents

- H01L2224/80895 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 3 patents

- H01L2224/80896 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 3 patents

- H01L21/4853 (Manufacture or treatment of parts, e.g. containers, prior to assembly of the devices, using processes not provided for in a single one of the subgroups): 2 patents

- H01L21/4857 (Manufacture or treatment of parts, e.g. containers, prior to assembly of the devices, using processes not provided for in a single one of the subgroups): 2 patents

- H01L23/49816 (Leads, {i.e. metallisations or lead-frames} on insulating substrates, {e.g. chip carriers (shape of the substrate): 2 patents

- H01L23/49822 ({Multilayer substrates (multilayer metallisation on monolayer substrate): 2 patents

- H01L23/49833 (Leads, {i.e. metallisations or lead-frames} on insulating substrates, {e.g. chip carriers (shape of the substrate): 2 patents

- H01L23/49838 (Leads, {i.e. metallisations or lead-frames} on insulating substrates, {e.g. chip carriers (shape of the substrate): 2 patents

- H01L24/16 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L24/32 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L24/73 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L2224/16238 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L2224/32225 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L2924/15311 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L24/09 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L2225/06541 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L2924/1431 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L23/3128 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L23/481 (Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements {; Selection of materials therefor}): 2 patents

- H01L25/105 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L2225/1035 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L2225/1041 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L2225/1058 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 2 patents

- H01L23/66 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L21/486 (Manufacture or treatment of parts, e.g. containers, prior to assembly of the devices, using processes not provided for in a single one of the subgroups): 1 patents

- H01L23/552 (Protection against radiation, e.g. light {or electromagnetic waves}): 1 patents

- H01L24/96 ({the devices being encapsulated in a common layer, e.g. neo-wafer or pseudo-wafer, said common layer being separable into individual assemblies after connecting}): 1 patents

- H01L24/97 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H10B80/00 (Assemblies of multiple devices comprising at least one memory device covered by this subclass): 1 patents

- H01L2223/6616 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2223/6672 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2224/16227 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2224/73204 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2224/95001 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2224/96 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2224/97 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2924/15174 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L23/585 ({comprising conductive layers or plates or strips or rods or rings (): 1 patents

- H01L23/5226 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L23/53295 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L29/0649 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L24/83 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L24/03 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L24/33 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L23/562 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2225/06568 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2225/06565 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2225/06593 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2225/06513 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2225/06524 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2224/94 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L21/565 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L25/0652 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2924/1434 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2225/06589 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2225/06586 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2224/08145 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2225/06582 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2224/08146 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L23/5385 (the interconnection structure between a plurality of semiconductor chips being formed on, or in, insulating substrates ({): 1 patents

- H01L2224/08225 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L23/3735 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L24/13 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L24/81 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L23/3185 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2224/13111 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2224/13139 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2224/13147 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2224/81193 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2224/81815 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2924/1517 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2924/3511 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L23/50 (for integrated circuit devices, {e.g. power bus, number of leads} (): 1 patents

- H01L23/5386 (the interconnection structure between a plurality of semiconductor chips being formed on, or in, insulating substrates ({): 1 patents

- H01L23/5389 (the interconnection structure between a plurality of semiconductor chips being formed on, or in, insulating substrates ({): 1 patents

- H01L24/17 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L24/19 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L24/20 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L24/48 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2224/04042 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2224/04105 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2224/12105 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2224/48091 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2224/48227 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2224/73265 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2224/73267 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2224/81385 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2924/00014 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2924/14 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L2924/181 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L21/481 (Manufacture or treatment of parts, e.g. containers, prior to assembly of the devices, using processes not provided for in a single one of the subgroups): 1 patents

- H01L21/56 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L25/0655 (SEMICONDUCTOR DEVICES NOT COVERED BY CLASS): 1 patents

- H01L24/06 ({of a plurality of bonding areas}): 1 patents

- H01L23/49503 (Lead-frames {or other flat leads (): 1 patents

- H01L23/49827 ({Via connections through the substrates, e.g. pins going through the substrate, coaxial cables (): 1 patents

- H03K19/1776 (PULSE TECHNIQUE (measuring pulse characteristics): 1 patents

Companies

List of Companies

- Taiwan Semiconductor Manufacturing Co., Ltd.: 8 patents

- Taiwan Semiconductor Manufacturing CO., Ltd.: 1 patents

Collaborators

- Ming-Fa Chen (6 collaborations)

- Shin-Puu Jeng (3 collaborations)

- Jie Chen (3 collaborations)

- Chieh-Lung Lai (2 collaborations)

- Meng-Liang Lin (2 collaborations)

- Chih-Chia Hu (2 collaborations)

- Chen-Hua Yu (2 collaborations)

- Chun-Yueh Yang (1 collaborations)

- Chun-Chiang Kuo (1 collaborations)

- Sen-Bor Jan (1 collaborations)

- Ying-Ju Chen (1 collaborations)

- Der-Chyang Yeh (1 collaborations)

Subcategories

This category has the following 5 subcategories, out of 5 total.

C

H

M

S

- Ming-Fa Chen

- Shin-Puu Jeng

- Jie Chen

- Chieh-Lung Lai

- Meng-Liang Lin

- Chih-Chia Hu

- Chen-Hua Yu

- Chun-Yueh Yang

- Chun-Chiang Kuo

- Sen-Bor Jan

- Ying-Ju Chen

- Der-Chyang Yeh

- Hsien-Wei Chen

- Inventors

- Inventors filing patents with Taiwan Semiconductor Manufacturing Co., Ltd.

- Inventors filing patents with Taiwan Semiconductor Manufacturing CO., Ltd.